LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output

You are here:

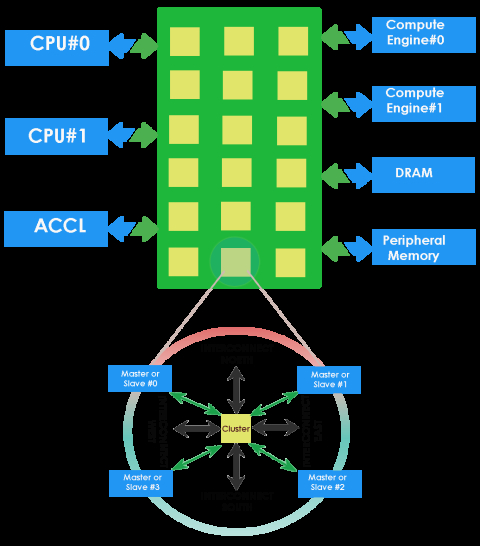

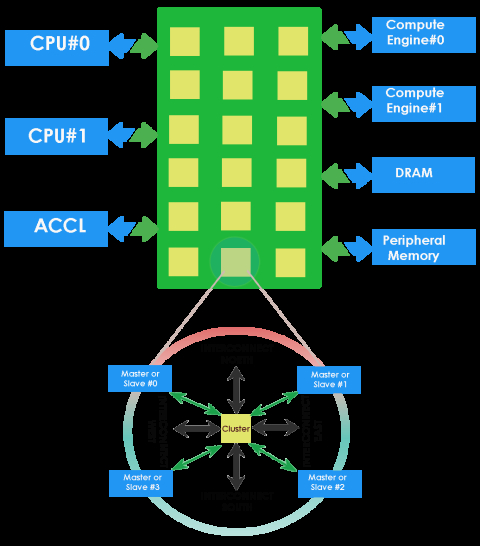

Coherent Network-on-chip (NoC) IP

C-NoC is a layered, scalable, configurable, and physically aware configurable NoC. It supports mesh, grid and torus topologies with simultaneous existence of both coherent and non-coherent traffic. It has configurable data bus widths, supports multiple clocking schemes, and is physically-aware with auto-pipelining and grouping of routers to meet timing requirements. C-NoC supports multiple protocols including CHI, AXI4/3 and AXI-lite, ACE and ACE-lite.

C-NoC provides power control through power-islanding and a power-gating architecture at the interface port and router level, and is physically aware with automated insertion and deletion of pipelines to meet timing, generation of placement-aware groups and topologies, and power and frequency aware NoC generation.

C-NoC provides high performance with on-chip L3 cache support to reduce memory access latency, and its pipeline architecture provides scalability with maximum throughput and minimum latency. It is parity enabled to provide resiliency.

C-NoC provides power control through power-islanding and a power-gating architecture at the interface port and router level, and is physically aware with automated insertion and deletion of pipelines to meet timing, generation of placement-aware groups and topologies, and power and frequency aware NoC generation.

C-NoC provides high performance with on-chip L3 cache support to reduce memory access latency, and its pipeline architecture provides scalability with maximum throughput and minimum latency. It is parity enabled to provide resiliency.

查看 Coherent Network-on-chip (NoC) IP 详细介绍:

- 查看 Coherent Network-on-chip (NoC) IP 完整数据手册

- 联系 Coherent Network-on-chip (NoC) IP 供应商

Block Diagram of the Coherent Network-on-chip (NoC) IP