You are here:

xSPI闪存控制器

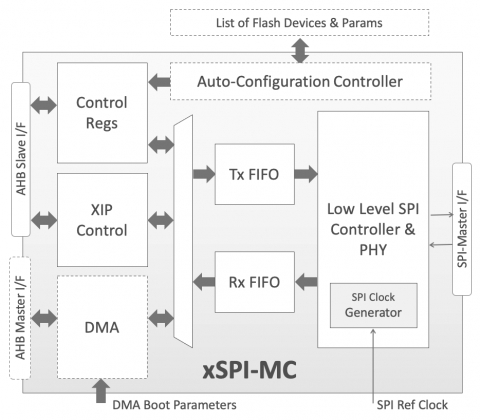

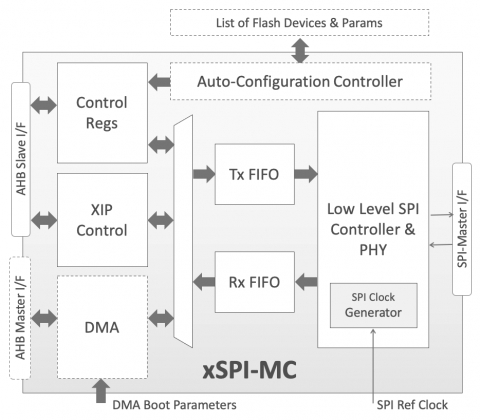

该内核允许系统按下列某个模式与一个或多个串行闪存设备接口:a)在从模式下,通过AHB从接口访问其寄存器; b)在DMA模式下,系统对内部DMA引擎进行编程,然后内核相应地驱动其AHB主接口; c)在eXecute In-Place(XIP)模式下,该内核允许系统通过AHB从接口直接访问SPI存储器地址空间; d)在Boot-Image引导映像复制模式下,在复位后,内核将使用其AHB主接口,自动将大量数据(Boot-Image引导映像)从SPI内存复制到AHB地址空间(例如,在影子RAM或DRAM上)。

该内核可与单,双,四,双四和八个SPI闪存设备一起工作。为了能够与来自不同供应商的闪存设备一起使用,该内核提供了两种配置设备特定参数的方式:a)通过寄存器,系统负责识别连接的闪存设备并将适当的参数值编程到内核的寄存器中; b)通过使用自动配置功能,内核将自动识别所连接的闪存设备并对其进行相应编程。自动配置功能使用一块用户提供的内存,该内存存储了可自动识别的设备及其功能的列表。

可以方便地配置xSPI-MC来匹配不同的应用需求。 AHB接口的数据和地址宽度,DMA引擎的实例化和自动配置逻辑,内核支持的最大Flash设备数量以及所有配置寄存器的复位值,是一些可以通过简单的Verilog定义进行控制的设计参数。此外,由于该内核具有可综合的软PHY,并且不使用任何特定于工艺的模块,因此可以轻松地由任何ASIC工艺来实现。

该内核是根据行业最佳实践设计的。它是LINT干净且可扫描的,已通过严格的验证,并且已通过流片验证。

该内核可与单,双,四,双四和八个SPI闪存设备一起工作。为了能够与来自不同供应商的闪存设备一起使用,该内核提供了两种配置设备特定参数的方式:a)通过寄存器,系统负责识别连接的闪存设备并将适当的参数值编程到内核的寄存器中; b)通过使用自动配置功能,内核将自动识别所连接的闪存设备并对其进行相应编程。自动配置功能使用一块用户提供的内存,该内存存储了可自动识别的设备及其功能的列表。

可以方便地配置xSPI-MC来匹配不同的应用需求。 AHB接口的数据和地址宽度,DMA引擎的实例化和自动配置逻辑,内核支持的最大Flash设备数量以及所有配置寄存器的复位值,是一些可以通过简单的Verilog定义进行控制的设计参数。此外,由于该内核具有可综合的软PHY,并且不使用任何特定于工艺的模块,因此可以轻松地由任何ASIC工艺来实现。

该内核是根据行业最佳实践设计的。它是LINT干净且可扫描的,已通过严格的验证,并且已通过流片验证。

查看 xSPI闪存控制器 详细介绍:

- 查看 xSPI闪存控制器 完整数据手册

- 联系 xSPI闪存控制器 供应商

Block Diagram of the xSPI闪存控制器