You are here:

Wide-Range Low-Area Digital PLL in TSMC 28HPM

Granite SemiCom Inc. (GSC) has just completed the design, layout, and verification, of it’s digitall PLL (DPLL) for realization in TSMC’s 28nm HPM process; this is GSC’s third DPLL (developed over the previous five years). Fabrication is currently scheduled for the second quarter of 2014. The intended applications are for general purpose, moderately high speed, clock generation applications where small area and power are critical without sacrificing quality. Previous generations (realized in TSMC’s 40G and 40LP processes) were intended for the highest speeds possible for a PLL based on a wide-frequency-range ring-oscillator necessitating higher power. The new DPLL28 has traded off speed for greatly minimized power and area, yet retaining excellent jitter for the intended speeds (rms period jitter less than 0.1% of the ouput period). An example application might be for generating a clock in a DDR3 controller or in the CMU for multi-lane chip-to-chip serial links where a large number of CMUs are required.

查看 Wide-Range Low-Area Digital PLL in TSMC 28HPM 详细介绍:

- 查看 Wide-Range Low-Area Digital PLL in TSMC 28HPM 完整数据手册

- 联系 Wide-Range Low-Area Digital PLL in TSMC 28HPM 供应商

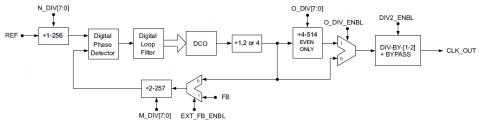

Block Diagram of the Wide-Range Low-Area Digital PLL in TSMC 28HPM

PLL IP

- TSMC CLN7FF 7nm Clock Generator PLL - 800MHz-4000MHz

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- Jitter Cleaner PLL Digital Loop Filter

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL