RISC-V Processor - RV12 - 32/64 bit, Single Core CPU

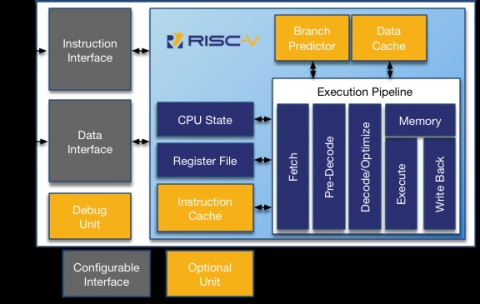

The RV12 implements a Harvard architecture for simultaneous instruction and data memory accesses. It features an optimizing folded 4-stage pipeline, which optimizes overlaps between the execution and memory accesses, thereby reducing stalls and improving efficiency.

Optional features include Branch Prediction, Instruction Cache, Data Cache, and Debug Unit. Parameterised and configurable features include the instruction and data interfaces, the branch-prediction-unit configuration, and the cache size, associativity, and replacement algorithms. Providing the user with trade offs between performance, power, and area to optimize the core for the application

查看 RISC-V Processor - RV12 - 32/64 bit, Single Core CPU 详细介绍:

- 查看 RISC-V Processor - RV12 - 32/64 bit, Single Core CPU 完整数据手册

- 联系 RISC-V Processor - RV12 - 32/64 bit, Single Core CPU 供应商

Block Diagram of the RISC-V Processor - RV12 - 32/64 bit, Single Core CPU

RISC-V Processor IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- ARC-V RHX-100 dual-issue, 32-bit single-core RISC-V processor for real-time applications

- 32-bit Embedded RISC-V Functional Safety Processor