You are here:

USB2.0 PHY, 8-bit or a 16-bit parallel interface, remaining backward compatible with USB1.1 legacy protocol at 12Mbps

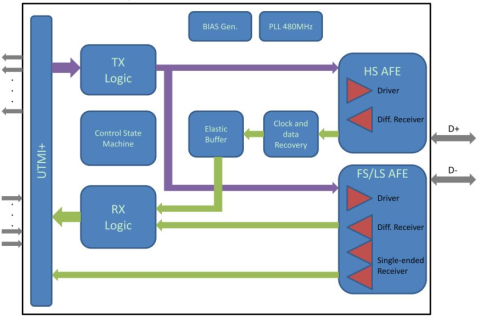

KA13UGUSB20ST001 is USB2.0 physical layer transceiver (PHY) integrated circuits. The PHY can be configured for either an 8-bit or a 16-bit parallel interface, which complies with the USB Transceiver Macrocell Interface (UTMI) specification. It supports 480bps transfer rate, while remaining backward compatible with USB1.1 legacy protocol at 12Mbps.

It includes the following blocks:

* Analog Driver and Receiver

* PLL generate the 480MHz clock

* Clock and Data Recovery

* NRZI encoder/decoder

* Serialize / De-serialize

* Control state machine

* Integrated pull up and self-calibrated termination resistors and switches

It includes the following blocks:

* Analog Driver and Receiver

* PLL generate the 480MHz clock

* Clock and Data Recovery

* NRZI encoder/decoder

* Serialize / De-serialize

* Control state machine

* Integrated pull up and self-calibrated termination resistors and switches

查看 USB2.0 PHY, 8-bit or a 16-bit parallel interface, remaining backward compatible with USB1.1 legacy protocol at 12Mbps 详细介绍:

- 查看 USB2.0 PHY, 8-bit or a 16-bit parallel interface, remaining backward compatible with USB1.1 legacy protocol at 12Mbps 完整数据手册

- 联系 USB2.0 PHY, 8-bit or a 16-bit parallel interface, remaining backward compatible with USB1.1 legacy protocol at 12Mbps 供应商

Block Diagram of the USB2.0 PHY, 8-bit or a 16-bit parallel interface, remaining backward compatible with USB1.1 legacy protocol at 12Mbps

USB 2.0 IP

- USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

- USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core

- USB 2.0 nanoPHY in SMIC (65nm)

- USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in TSMC 22ULP

- USB 2.0 PHY IP, Silicon Proven in TSMC 22ULP