三速串行数字接口(SDI)物理层(PHY) IP核

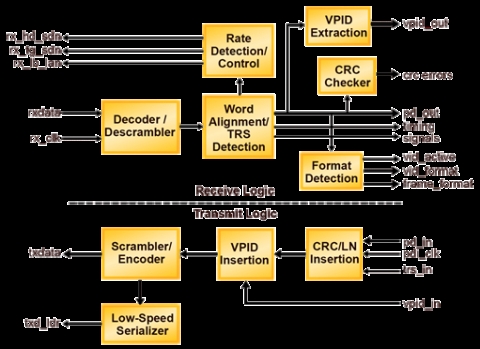

莱迪思的三速SDI PHY IP (知识产权)核是一个完整的SDI PHY接口,一端连接到高速SDI串行数据(通过LatticeECP3™ SERDES),并在另一端对并行视频数据进行格式化。它可以实现更快的应用开发,用于处理、储存和桥接SDI视频数据。它由以下主要的功能模块组成:SDI编码器/解码器、字对齐、CRC检测和检查、VPID(视频负载识别码)的插入和提取,以及速率检测逻辑。IP核支持以下由电影电视工程师协会(Society for Motion Picture and Television Engineers,SMPTE)颁布的SDI接口标准和源格式。

* 接口:SMPTE 259M-2006 [1] (SD)、SMPTE 292M-1998 [2] (HD)和SMPTE 424 M [3] (3G)

* SD源格式:SMPTE 125M [4]和SMPTE 267M [5] (仅13.5 Mhz)

* HD源格式:SMPTE 260M [6]、SMPTE 274M [7]、SMPTE 295M [8]和SMPTE 296M [9]

* 3G源格式:SMPTE 425M [10]

当该IP与LatticeECP3 SERDES连接后,可以通过一个通用的物理串行接口,发送和/或接收任何支持的视频标准和格式。IP核可以自动扫描并锁定到任何支持的视频流。接收多种标准的视频格式需要应用提供适当的外部时钟来响应IP核的指令。

查看 三速串行数字接口(SDI)物理层(PHY) IP核 详细介绍:

- 查看 三速串行数字接口(SDI)物理层(PHY) IP核 完整数据手册

- 联系 三速串行数字接口(SDI)物理层(PHY) IP核 供应商

Block Diagram of the 三速串行数字接口(SDI)物理层(PHY) IP核

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software