You are here:

Tessent RISC-V 追踪和调试

Tessent UltraSight-V 是 Tessent 嵌入式分析产品系列的一部分,是基于 RISC-V 的 SoC 的全面解决方案。UltraSight-V 结合了嵌入式 IP 和软件,使嵌入式软件工程师能够更加高效地开发高性能嵌入式软件。利用基于高效跟踪 (E-trace) 标准的有效、非侵入式技术和处理器跟踪技术,该解决方案可最大限度地减少调试延迟,加快 SoC 项目进度,确保项目按期上市。

Tessent 增强型追踪编码器是市场领先的 RISC-V 追踪解决方案。它是一款全功能解决方案,提供了实时监控 CPU 程序执行情况的机制。它对程序执行进行编码(指令追踪),还可以选择对来自加载和存储指令的数据进行编码(数据追踪),以高度压缩的格式输出追踪。

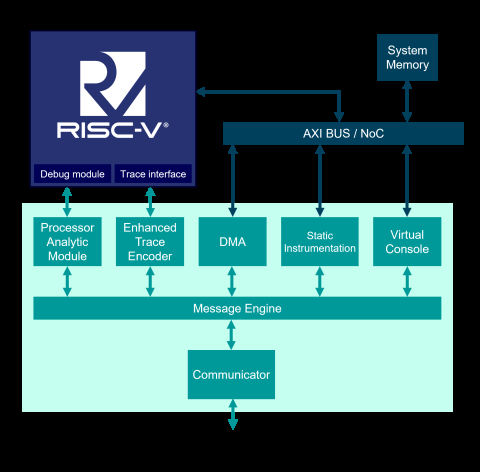

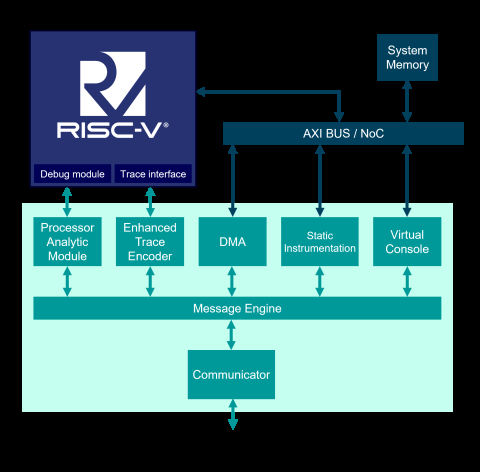

Tessent UltraSight-V 包含一组 IP 模块,这些模块能够提供深入的可见性,使用户能够了解软件在系统中的具体行为和表现。处理器分析 (PAM) IP 模块提供运行控制功能。 利用直接内存访问 (DMA) IP 模块,代码上传到系统级芯片 (SoC) 的速度比使用普通 GDB 加载快 70-100 倍。 利用静态插桩 IP 模块,可以用少 20 倍的指令完成带时间戳的 printf 风格的调试。 虚拟控制台模块为目标设备上运行的软件和调试主机之间提供了一个双向通信通道。它取代了基于 UART 的传统通信,无需额外的物理端口。 所有 IP 模块均可在系统运行时进行编程。

Tessent UltraSight-V 的增强型跟踪编码器 (ETE) 提供了一种实时监控 CPU 程序执行的机制。它对指令执行进行编码,并可选择对数据内存访问进行编码,然后以高度压缩的格式输出数据。设备执行可以完全离线重建。西门子是 RISC-V 高效跟踪 (E-Trace) 标准的主要贡献者之一,我们的增强型跟踪编码器支持 E-Trace 规范中的所有必选和可选功能。它还提供了周期精确的跟踪,这简化了软件性能优化。

Tessent UltraSight-V 包含灵活的 Host Suite 软件环境,支持命令行、脚本和基于集成开发环境 (IDE) 的调试以及与 IP 模块的交互。

Tessent 增强型追踪编码器是市场领先的 RISC-V 追踪解决方案。它是一款全功能解决方案,提供了实时监控 CPU 程序执行情况的机制。它对程序执行进行编码(指令追踪),还可以选择对来自加载和存储指令的数据进行编码(数据追踪),以高度压缩的格式输出追踪。

Tessent UltraSight-V 包含一组 IP 模块,这些模块能够提供深入的可见性,使用户能够了解软件在系统中的具体行为和表现。处理器分析 (PAM) IP 模块提供运行控制功能。 利用直接内存访问 (DMA) IP 模块,代码上传到系统级芯片 (SoC) 的速度比使用普通 GDB 加载快 70-100 倍。 利用静态插桩 IP 模块,可以用少 20 倍的指令完成带时间戳的 printf 风格的调试。 虚拟控制台模块为目标设备上运行的软件和调试主机之间提供了一个双向通信通道。它取代了基于 UART 的传统通信,无需额外的物理端口。 所有 IP 模块均可在系统运行时进行编程。

Tessent UltraSight-V 的增强型跟踪编码器 (ETE) 提供了一种实时监控 CPU 程序执行的机制。它对指令执行进行编码,并可选择对数据内存访问进行编码,然后以高度压缩的格式输出数据。设备执行可以完全离线重建。西门子是 RISC-V 高效跟踪 (E-Trace) 标准的主要贡献者之一,我们的增强型跟踪编码器支持 E-Trace 规范中的所有必选和可选功能。它还提供了周期精确的跟踪,这简化了软件性能优化。

Tessent UltraSight-V 包含灵活的 Host Suite 软件环境,支持命令行、脚本和基于集成开发环境 (IDE) 的调试以及与 IP 模块的交互。

查看 Tessent RISC-V 追踪和调试 详细介绍:

- 查看 Tessent RISC-V 追踪和调试 完整数据手册

- 联系 Tessent RISC-V 追踪和调试 供应商

Block Diagram of the Tessent RISC-V 追踪和调试

RISC-V IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- ARC-V RHX-100 dual-issue, 32-bit single-core RISC-V processor for real-time applications

- 32-bit Embedded RISC-V Functional Safety Processor