You are here:

Superscalar Out-of-Order Execution Multicore Cluster

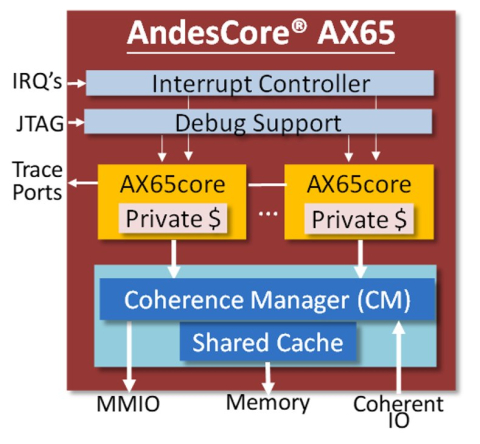

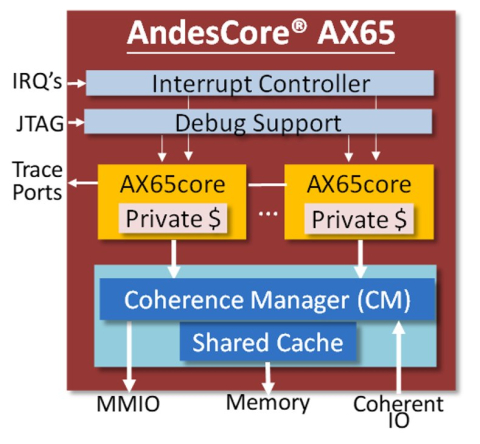

AndesCore™ AX65 64-bit multicore CPU IP is a high-performance quad decode 13-stage superscalar out-of-order processor based on AndeStar™ V5 architecture. It supports RISC-V standard “G (IMA-FD)”, “C” 16-bit compression, “B” bit manipulation, “K” (scalar crypto), CMO extensions, and Andes performance enhancements. It features MMU for Linux based applications, TAGE branch prediction for accurate branch execution, 4 wide instruction decode, 8 independent functional pipelines (4 integer, 2 fp, 2 load/store), level-1 instruction/data caches for low-latency accesses. The AX65 symmetric multiprocessor supports up to eight cores and a level-2 cache controller with instruction and data prefetch. Coherence Manger ensures data coherence among CPU accesses and IO transactions from cacheless bus masters. Other features include ECC for level-1/2 memory soft error protection, Platform-Level Interrupt Controller (PLIC) with enhancements for vectored dispatch and priority-based preemption, StackSafe™, and PowerBrake and WFI for power management.

查看 Superscalar Out-of-Order Execution Multicore Cluster 详细介绍:

- 查看 Superscalar Out-of-Order Execution Multicore Cluster 完整数据手册

- 联系 Superscalar Out-of-Order Execution Multicore Cluster 供应商

Block Diagram of the Superscalar Out-of-Order Execution Multicore Cluster

RISC-V; superscalar;dual-issue;8-stage pipeline;microprocessor;64-bit IP

- 64-Bit 8-stage superscalar processor that supports RISC-V specification, including GCN

- 64-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCN

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP (DSP)

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

- 64-bit RISC-V Multicore Processor with 1024-bit Vector Extension