Simple Micro APB Bus Controller

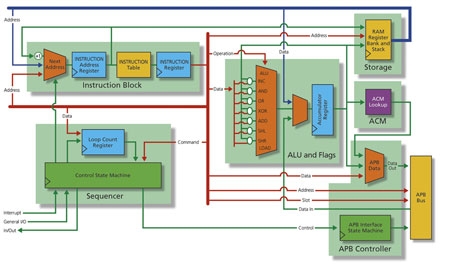

The core consists of six main blocks:

* Instruction block

* Sequencer

* ALU and flags

* Storage

* ACM

* APB controller

* AMBA3 APB master interface controller

查看 Simple Micro APB Bus Controller 详细介绍:

- 查看 Simple Micro APB Bus Controller 完整数据手册

- 联系 Simple Micro APB Bus Controller 供应商

Block Diagram of the Simple Micro APB Bus Controller

Simple Micro APB Bus Controller IP

- CAN 2.0 & CAN FD Bus Controller IP

- Direct Memory Access Controller IP Core

- I2C Host / Device Bus Controller

- Configurable CAN Bus Controller IP with Flexible Data-Rate

- SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption)

- I2C Controller (AMBA APB <-> I2C)