High Capacity Post-Quantum Cryptography Processor (PQF-HW-LAT)

You are here:

SFI-5

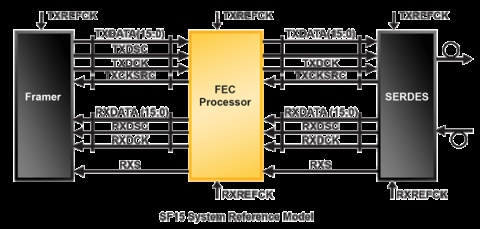

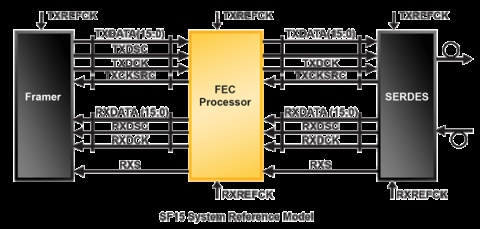

The SFI-5 Intellectual Property (IP) core enables user instantiation of an OIF-compliant SERDES Framer Interface Level 5 (SFI-5) core in LatticeSC/M Field Programmable Gate Arrays (FPGAs). The SFI-5 System Reference Model is shown in the figure below. The SFI-5 defines a communications interface for a 40 Gbps optical link which typically consists of a Framer, FEC (Forward Error Correction) Processor, and SERDES. The purpose of the SFI-5 interface is to transmit data across multiple channels in parallel, where channels may incur different skews between the transmitter and receivers. The SFI-5 receiver delays the data received on all of the channels to match that channel which incurred the longest delay. This removes any skew variation between the channels.

The SFI-5 interface uses 16 bi-directional SERDES links to transmit and receive data. Another SERDES link (the 17th channel) is used as the Deskew channel.

The SFI-5 is a user-configurable IP core, which allows the configuration of the IP and generation of a netlist and simulation file for use in designs. Please note that bitstream generation may be prevented or the bitstream may have time logic present unless a license for the IP is procured.

SFI-5 IP User's Guide The LatticeSC SFI-5 IP Core User's Guide is now available.

SFI-5 Evaluation Board The LatticeSC SFI-5 Evaluation Board is a functional platform for development and rapid prototyping of applications that incorporate high-performance SFI-5 interfaces available for SFI-5 evaluation.

SFI-5 Reference Design The reference design included with the SFI-5 IP package (sfi5_eval directory) is designed for use on the LatticeSC SFI-5 Evaluation Board.

The SFI-5 interface uses 16 bi-directional SERDES links to transmit and receive data. Another SERDES link (the 17th channel) is used as the Deskew channel.

The SFI-5 is a user-configurable IP core, which allows the configuration of the IP and generation of a netlist and simulation file for use in designs. Please note that bitstream generation may be prevented or the bitstream may have time logic present unless a license for the IP is procured.

SFI-5 IP User's Guide The LatticeSC SFI-5 IP Core User's Guide is now available.

SFI-5 Evaluation Board The LatticeSC SFI-5 Evaluation Board is a functional platform for development and rapid prototyping of applications that incorporate high-performance SFI-5 interfaces available for SFI-5 evaluation.

SFI-5 Reference Design The reference design included with the SFI-5 IP package (sfi5_eval directory) is designed for use on the LatticeSC SFI-5 Evaluation Board.

查看 SFI-5 详细介绍:

- 查看 SFI-5 完整数据手册

- 联系 SFI-5 供应商

Block Diagram of the SFI-5

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software