Universal Chiplet Interconnect Express (UCIe 1.0) Controller

You are here:

串行FIR滤波器

许多数字系统使用滤波器来消除噪声、频谱整形,或进行信号检测。提供这些功能的两种常见的滤波器是无限脉冲响应(IIR)和有限脉冲响应(FIR)滤波器。系统中使用的IIR滤波器可以容忍相位失真。 FIR滤波器有固有的稳定结构,系统中使用的FIR滤波器需要有线性相位。这些优点使FIR滤波器有足够的吸引力,因此在大量的系统中使用了FIR滤波器设计。但是,对于给定的频率响应规范,FIR滤波器比IIR高阶,使其计算开销很高。

莱迪思的串行FIR滤波器使用串行运算单元实现了紧凑的结构。由于算法的串行特性,数据速率比时钟速率慢,取决于数据宽度。有效吞吐量定义为:

数据传输速率 = (f/(ofw +1)

OFW是输出的宽度,F是时钟频率。

莱迪思的串行FIR滤波器使用串行运算单元实现了紧凑的结构。由于算法的串行特性,数据速率比时钟速率慢,取决于数据宽度。有效吞吐量定义为:

数据传输速率 = (f/(ofw +1)

OFW是输出的宽度,F是时钟频率。

查看 串行FIR滤波器 详细介绍:

- 查看 串行FIR滤波器 完整数据手册

- 联系 串行FIR滤波器 供应商

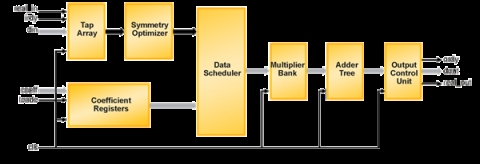

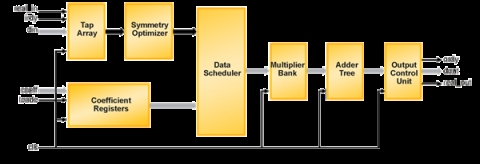

Block Diagram of the 串行FIR滤波器

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software