You are here:

Scalable Ultra-High Throughput DSC 1.2b Encoder

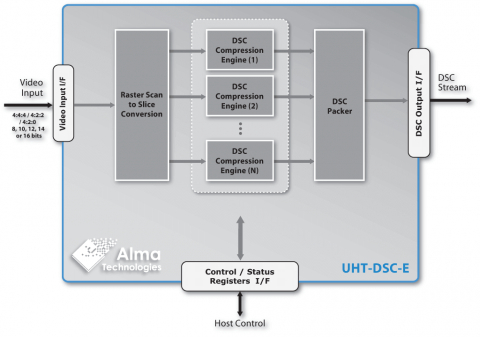

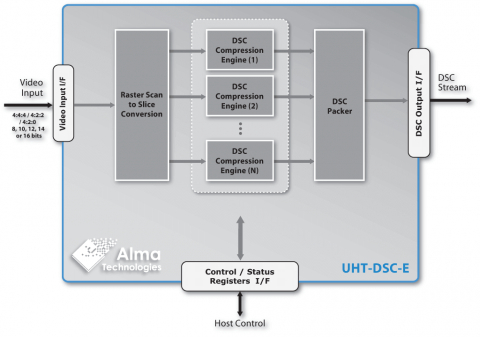

The UHT-DSC-E core is a scalable, ultra-high throughput, advanced DSC 1.2b encoder, compliant to the VESA Display Stream Compression (DSC) 1.2b standard. It supports encoding of 4:4:4, 4:2:2 and 4:2:0 video streams, in 8 to 16 bits per component color depths.

The core is designed for enabling ultra-high frame rate SD, HD and Ultra HD video encoding up to 10K resolutions, even in medium-end ASIC or FPGA silicon. The scalability of this IP core enables highly cost-effective silicon implementations of applications that need to handle massive pixel rates and resolutions. The UHT-DSC-E is available for ASIC or Intel, Lattice, Microsemi and Xilinx FPGA and SoC based designs.

The UHT-DSC-E is very easy to use and integrate in a system, designed for using only internal memory blocks and with simple, fully controllable and FIFO-like, streaming input and output interfaces. It requires minimal host intervention as it only needs to be programmed once per video sequence. Once programmed, it can encode an arbitrary number of video frames without the need of any further intervention or assistance by the host system CPU.

The core is designed for enabling ultra-high frame rate SD, HD and Ultra HD video encoding up to 10K resolutions, even in medium-end ASIC or FPGA silicon. The scalability of this IP core enables highly cost-effective silicon implementations of applications that need to handle massive pixel rates and resolutions. The UHT-DSC-E is available for ASIC or Intel, Lattice, Microsemi and Xilinx FPGA and SoC based designs.

The UHT-DSC-E is very easy to use and integrate in a system, designed for using only internal memory blocks and with simple, fully controllable and FIFO-like, streaming input and output interfaces. It requires minimal host intervention as it only needs to be programmed once per video sequence. Once programmed, it can encode an arbitrary number of video frames without the need of any further intervention or assistance by the host system CPU.

查看 Scalable Ultra-High Throughput DSC 1.2b Encoder 详细介绍:

- 查看 Scalable Ultra-High Throughput DSC 1.2b Encoder 完整数据手册

- 联系 Scalable Ultra-High Throughput DSC 1.2b Encoder 供应商

Block Diagram of the Scalable Ultra-High Throughput DSC 1.2b Encoder

VESA DSC IP

- VESA DSC (Display Stream Compression) 1.2b Video Encoder

- VESA DSC (Display Stream Compression) 1.2b Video Decoder

- ASIL-B Ready ISO 26262 Certified VESA DSC (Display Stream Compression) 1.1 Encoder

- VESA DisplayPort 1.4 RX IP Subsystem for Xilinx FPGAs

- VESA DSC 1.2b Encoder for Xilinx FPGAs

- VESA DSC 1.2b Decoder IP Core for Xilinx FPGAs