Register File with low power retention mode and 3 speed options

You are here:

RISC-V-based SoC template

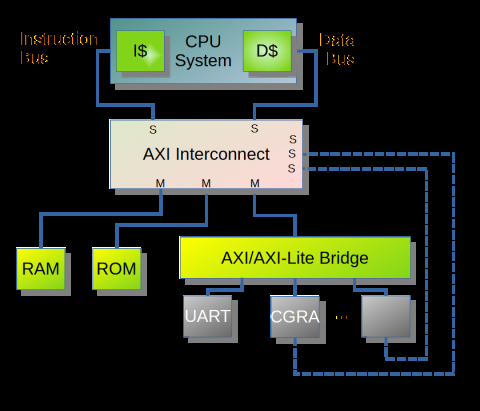

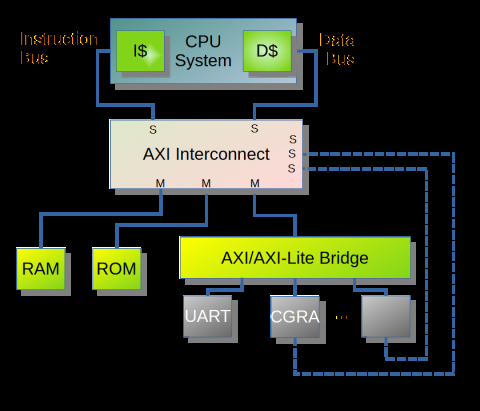

IOb-SoC is a RISC-V SoC that can be configured in Python and generated in Verilog, The core is open-source and can be downloaded from https://github.com/IObundle/iob-soc

查看 RISC-V-based SoC template 详细介绍:

- 查看 RISC-V-based SoC template 完整数据手册

- 联系 RISC-V-based SoC template 供应商

Block Diagram of the RISC-V-based SoC template

RISC-V IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- ARC-V RHX-100 dual-issue, 32-bit single-core RISC-V processor for real-time applications

- 32-bit Embedded RISC-V Functional Safety Processor