You are here:

Register Indirect RAM Access

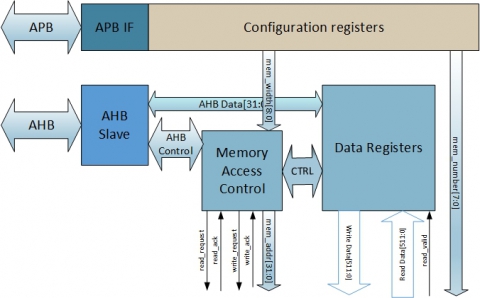

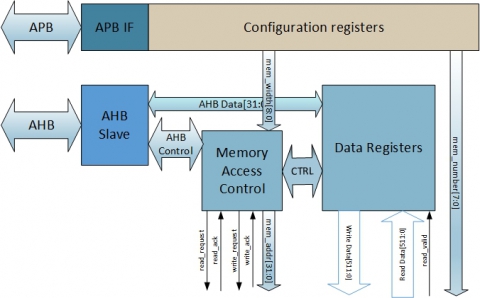

The Veriest Register Indirect RAM Access Design IP provides a bridge between the embedded AMBA AHB bus and a configurable number of embedded SRAM devices for test, initialization and other low bandwidth purposes. The Veriest Register Indirect RAM Access is ideal for IP developers to provide access to shared RAMs in which the CPU needs to have limited access whereas another RAM client has priority access. After a simple register configuration setup by the CPU, the RAMs can be accessed for read and write through the AHB slave interface.

查看 Register Indirect RAM Access 详细介绍:

- 查看 Register Indirect RAM Access 完整数据手册

- 联系 Register Indirect RAM Access 供应商

Block Diagram of the Register Indirect RAM Access