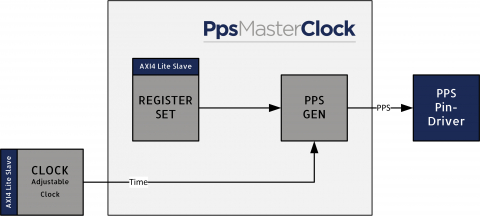

Pulse Per Second Master (PPS) core

All calculations and corrections are implemented completely in HW.

查看 Pulse Per Second Master (PPS) core 详细介绍:

- 查看 Pulse Per Second Master (PPS) core 完整数据手册

- 联系 Pulse Per Second Master (PPS) core 供应商

Block Diagram of the Pulse Per Second Master (PPS) core