You are here:

PLL 3.2GHz

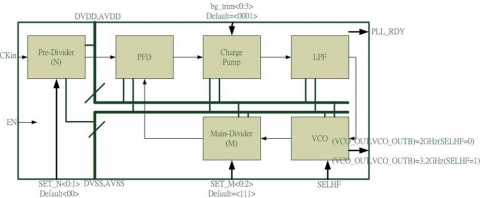

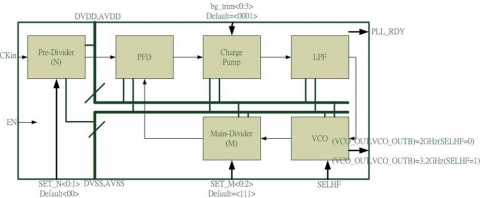

This IP is a phase locked loop which base on TSMC 40nm. It integrates a Phase Frequency detector (PFD), a Charge Pump (CP), a Low Pass Filter (LPF), a Voltage Control Oscillator (VCO) and other associated blocks. All fundamental building blocks as well as fully programmable dividers are integrated on the core. It is developed as a macro cell for clock generator and frequency synthesizer. The output frequency can be up to 3.2GHz. This IP supports operation voltage is 1.1V.

查看 PLL 3.2GHz 详细介绍:

- 查看 PLL 3.2GHz 完整数据手册

- 联系 PLL 3.2GHz 供应商

Block Diagram of the PLL 3.2GHz

PLL IP

- TSMC CLN7FF 7nm Clock Generator PLL - 800MHz-4000MHz

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- Jitter Cleaner PLL Digital Loop Filter

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL