You are here:

PCIe Multifunction IP Core for Intel FPGAs

The PCI Express specification allows endpoints

that incorporate more than one physical PCIe

function. Such endpoints are called

multifunction devices. The big advantage of a

multifunction device is, that a separate device

driver can be associated to each physical

function. This simplifies driver development and

maintenance significantly by separating the

peripheral functions logically into different

device drivers.

The Intel PCIe hardblocks in the Cyclone V /

Arria V FPGA device families support multifunction devices natively but on a very low

level.

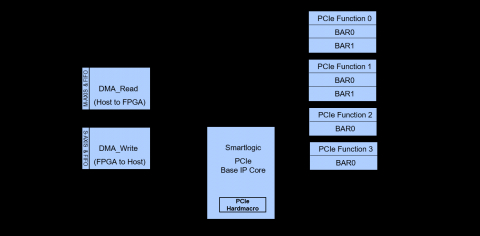

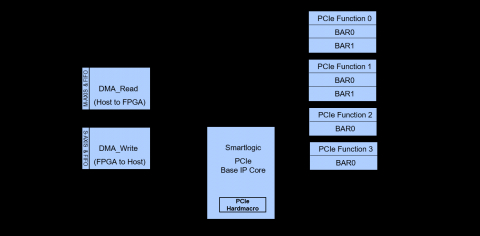

Smartlogic’s PCI Express multifunction IP core

for Cyclone V FPGAs offers a fully productized

IP core with optional DMA support. The core

operates with industry standard interfaces (AXI

and AXI Stream) and encapsulates the whole

PCI Express protocol know-how. This frees the

FPGA designer to concentrate on the project

specific design tasks.

that incorporate more than one physical PCIe

function. Such endpoints are called

multifunction devices. The big advantage of a

multifunction device is, that a separate device

driver can be associated to each physical

function. This simplifies driver development and

maintenance significantly by separating the

peripheral functions logically into different

device drivers.

The Intel PCIe hardblocks in the Cyclone V /

Arria V FPGA device families support multifunction devices natively but on a very low

level.

Smartlogic’s PCI Express multifunction IP core

for Cyclone V FPGAs offers a fully productized

IP core with optional DMA support. The core

operates with industry standard interfaces (AXI

and AXI Stream) and encapsulates the whole

PCI Express protocol know-how. This frees the

FPGA designer to concentrate on the project

specific design tasks.

查看 PCIe Multifunction IP Core for Intel FPGAs 详细介绍:

- 查看 PCIe Multifunction IP Core for Intel FPGAs 完整数据手册

- 联系 PCIe Multifunction IP Core for Intel FPGAs 供应商

Block Diagram of the PCIe Multifunction IP Core for Intel FPGAs

PCIe IP

- PCIe 5.0 Integrity and Data Encryption Security Module

- PCIe 6.1 Controller

- PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency

- 56G Serdes in 7nm bundled with PCie Gen 5 controller IP