Secure-IC's Securyzr™ Fully Digital Physically Unclonable Function (PUF) - PQC Ready

You are here:

MIPI CSI-2 Controller Core

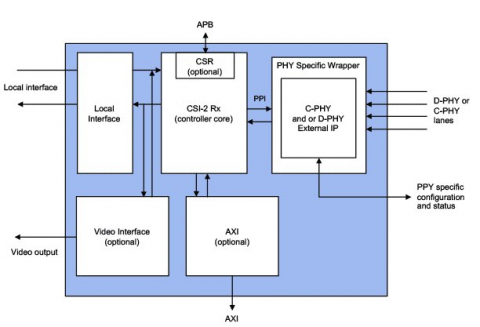

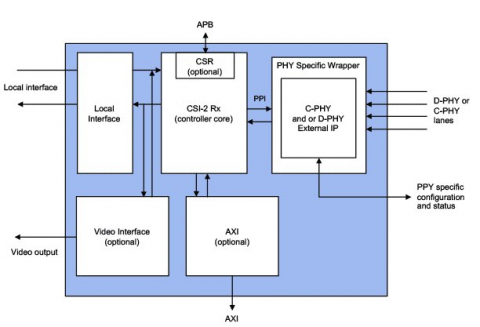

The Rambus CSI-2 Controller Core V2 is the second generation CSI-2 controller core. It is further optimized for high performance, low power and small size.

It is available in 64 and 32 bit core widths. The 64 bit core width can support 1-8 D-PHY data lanes (8 bit PPI) and 1-4 CPHY lanes (16 bit PPI). The 32 bit core width can support 1-4 D -PHY data lanes (8 bit PPI) and 1-2 C-PHY lanes (16 bit PPI) The core implements all three layers defined by the CSI-2 standard: Pixel to Byte Packing, Low Level Protocol, and Lane Management and is fully compliant with the CSI-2 standard. Separate Transmit (Tx) and Receive (Rx) versions of the core are available.

The core’s Local Interface is an easy to use pixel based interface (single, double, quad, octal pixel wide). An optional Hsync/Vsync Video Interface wrapper is also available. The core is delivered fully integrated and verified with the user’s target D/C-PHY. Contact Rambus for a complete list of supported PHYs.

The core is also provided with the CSI-2 Testbench which provides a CSI-2 Bus Functional Model.

Rambus offers a CSI-2 Demonstration System which includes an FPGA Board, MIPI Interface Card and MIPI Camera. Contact Rambus for more information.

Rambus also provides IP Core customization services. Contact Rambus for a quote.

It is available in 64 and 32 bit core widths. The 64 bit core width can support 1-8 D-PHY data lanes (8 bit PPI) and 1-4 CPHY lanes (16 bit PPI). The 32 bit core width can support 1-4 D -PHY data lanes (8 bit PPI) and 1-2 C-PHY lanes (16 bit PPI) The core implements all three layers defined by the CSI-2 standard: Pixel to Byte Packing, Low Level Protocol, and Lane Management and is fully compliant with the CSI-2 standard. Separate Transmit (Tx) and Receive (Rx) versions of the core are available.

The core’s Local Interface is an easy to use pixel based interface (single, double, quad, octal pixel wide). An optional Hsync/Vsync Video Interface wrapper is also available. The core is delivered fully integrated and verified with the user’s target D/C-PHY. Contact Rambus for a complete list of supported PHYs.

The core is also provided with the CSI-2 Testbench which provides a CSI-2 Bus Functional Model.

Rambus offers a CSI-2 Demonstration System which includes an FPGA Board, MIPI Interface Card and MIPI Camera. Contact Rambus for more information.

Rambus also provides IP Core customization services. Contact Rambus for a quote.

查看 MIPI CSI-2 Controller Core V2 详细介绍:

- 查看 MIPI CSI-2 Controller Core V2 完整数据手册

- 联系 MIPI CSI-2 Controller Core V2 供应商

Block Diagram of the MIPI CSI-2 Controller Core V2

MIPI CSI-2 Controller IP

- MIPI CSI-2 controller Receiver v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI CSI-2 RX Controller for v2.1

- MIPI CSI-2 TX Controller for v2.1

- MIPI CSI-2 RX Controller

- MIPI CSI2 Transmit Controller