You are here:

Low Power Clock Multiplier PLL for 40nm TSMC ULP CMOS

The OT3135 is a flexible low power clock multiplier PLL function with a wide range of input and output frequencies, and is designed for TSMC 40nm, ULP CMOS processes.

查看 Low Power Clock Multiplier PLL for 40nm TSMC ULP CMOS 详细介绍:

- 查看 Low Power Clock Multiplier PLL for 40nm TSMC ULP CMOS 完整数据手册

- 联系 Low Power Clock Multiplier PLL for 40nm TSMC ULP CMOS 供应商

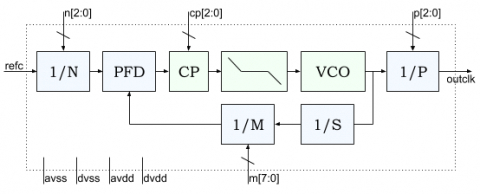

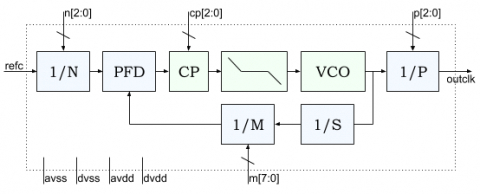

Block Diagram of the Low Power Clock Multiplier PLL for 40nm TSMC ULP CMOS

PLL IP

- TSMC CLN7FF 7nm Clock Generator PLL - 800MHz-4000MHz

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- Jitter Cleaner PLL Digital Loop Filter

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL