You are here:

LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output

The LDO IP is a 1.2V low-quiescent-current adjustable output voltage Low-Drop-Out (LDO) Linear Regulator implemented in the TSMC 3nm N3P CMOS process technology. Its low sleep current, 30 mA maximum current, output voltage adjustability and precision make it especially suitable for use as an integrated voltage regulation source for subsystems implemented in analog, digital, mixed-signal and RF ASICs and SoCs.

查看 LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output 详细介绍:

- 查看 LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output 完整数据手册

- 联系 LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output 供应商

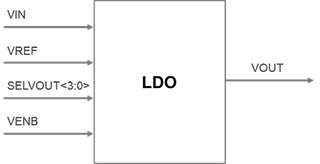

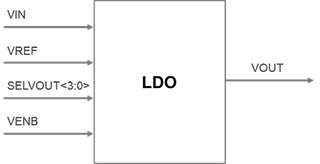

Block Diagram of the LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output

LDO IP

- LDO Voltage Regulator, 250 mA, Adjustable 0.45 V to 0.9 V Output

- Analog Front End: 2x 12-bit 4 GSPS IQ ADCs, 2x 12-bit 8GSPS IQ DACs, bandgap, temp sensor, PLL, 4 x LDO

- LDO Linear Voltage Regulator

- Ultra-low quiescent LDO voltage regulator in TSMC 22ULL

- Capless 1.8V output LDO with 2.0-3.6V input range - 0.18 EF

- Analog Front End: 8x 12-bit 2 GSPSADCs, 4x 12-bit 200 MSPS ADCs, TVM, PLL, LDO