You are here:

ISO 7816 Based Smart Card Reader

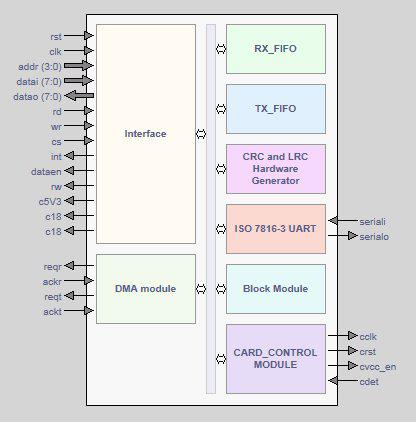

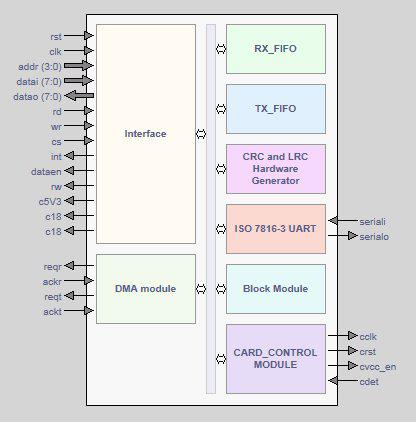

The DSMART is a fast, versatile and cost-competitive core intended for smart card reader applications. It provides a communication interface with a smart card, based on ISO 7816-3/EMV4.2 requirements. DCD’s IP Core implements the hardware support for both T0 character oriented protocol and T1 block oriented protocol. It’s been designed to combine highly reduced CPU utilization and low area consumption, it is able to activate and deactivate cards, perform resets, handle ATR reception and many additional features. Configuration options enable user to adjust the DSMART to his needs and choose the proprietary options, which will be the most suitable for his design. Data transfer to and from the host system can be interrupt-driven or executed through Direct Memory Access (DMA). The automatic convention detection and decoding mechanism ensure the exact result regardless of the used convention. Elementary Time Unit (ETU) - time duration of the one bit is decoded from the received ATR interface byte and generated automatically. The card clock divider provides non-gated clock with a wide range of possible frequencies. There’s been also a special power down mode implemented, in which the card clock is being hold in two possible states, depending on the card parameter. Error signaling and character repetition are automatic for the T0 protocol. The DSMART incorporates also an optional CRC/LRC hardware checking and generation mechanism which gives the convention independent result. The received CRC/LRC is not stored in the FIFO, but can be read in a case of CRC/LRC error. Also the optional block length counter provides security of the DMA block transfer and automatic CRC/LRC, subjoining with a manual affixing option. The special block mode handles block transfer automatically. Status and error registers provide necessary information about the FIFO state, errors and card events.

查看 ISO 7816 Based Smart Card Reader 详细介绍:

- 查看 ISO 7816 Based Smart Card Reader 完整数据手册

- 联系 ISO 7816 Based Smart Card Reader 供应商

Block Diagram of the ISO 7816 Based Smart Card Reader

Smart Card Reader IP

- Smart Card Reader Controller Core

- ISO 7816 based Smart Card Reader IP

- ISO 7816 based digital controller for integrated circuit card compliant with ETSI TS 102 221 and EMV 2000 standards

- IEC 7816 Smart Card IP

- I2C Master / Slave Controller with FIFO (AXI & AXI-Lite Bus)

- ISO/IEC 7816-3 digital controller for interface device compliant with ETSI TS 102 221 and EMV 2000 standards