MIPI CSI DSI C-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

You are here:

IEEE 802.11 n/ac/ax LDPC Encoder

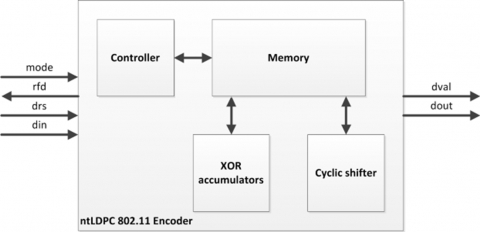

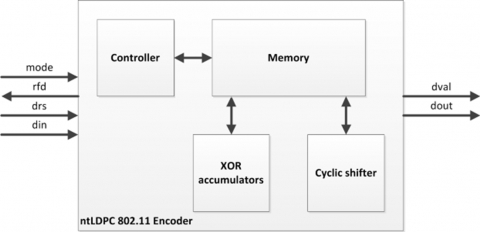

The Low Density Parity Check (LDPC) codes are powerful, capacity approaching channel codes and have exceptional error correction capabilities. The high degree of parallelism that they offer enables efficient, high throughput hardware architectures.

The ntLDPC_80211 IP Core is based on an implementation of QC-LDPC Quasi-Cyclic LDPC Codes. These LDPC codes are based on block-structured LDPC codes with circular block matrices. The entire parity check matrix can be partitioned into an array of block matrices; each block matrix is either a zero matrix or a right cyclic shift of an identity matrix. The parity check matrix designed in this way can be conveniently represented by a base matrix represented by cyclic shifts. The main advantage of this feature is that they offer high throughput at low implementation complexity.

The ntLDPC_80211 decoder IP Core may optionally implement one of two approximations of the log-domain LDPC iterative decoding algorithm (Belief propagation) known as either Layered Normalized Offset Min-Sum Algorithm or Layered Lambda-min Algorithm. Selecting between the two algorithms presents a decoding performance .vs. system resources utili-zation trade-off. The core is highly reconfigurable and fully compliant to the IEEE 802.11 n/ac/ax Wi-Fi4, Wi-Fi5 and Wi-Fi 6 standards.

The ntLDPC_80211 IP Core is based on an implementation of QC-LDPC Quasi-Cyclic LDPC Codes. These LDPC codes are based on block-structured LDPC codes with circular block matrices. The entire parity check matrix can be partitioned into an array of block matrices; each block matrix is either a zero matrix or a right cyclic shift of an identity matrix. The parity check matrix designed in this way can be conveniently represented by a base matrix represented by cyclic shifts. The main advantage of this feature is that they offer high throughput at low implementation complexity.

The ntLDPC_80211 decoder IP Core may optionally implement one of two approximations of the log-domain LDPC iterative decoding algorithm (Belief propagation) known as either Layered Normalized Offset Min-Sum Algorithm or Layered Lambda-min Algorithm. Selecting between the two algorithms presents a decoding performance .vs. system resources utili-zation trade-off. The core is highly reconfigurable and fully compliant to the IEEE 802.11 n/ac/ax Wi-Fi4, Wi-Fi5 and Wi-Fi 6 standards.

查看 IEEE 802.11 n/ac/ax LDPC Encoder 详细介绍:

- 查看 IEEE 802.11 n/ac/ax LDPC Encoder 完整数据手册

- 联系 IEEE 802.11 n/ac/ax LDPC Encoder 供应商

Block Diagram of the IEEE 802.11 n/ac/ax LDPC Encoder

WiFi6 IP

- Dual channel 12-bit, 1GS/s ADC in Samsung 8nm for 5G & WIFI6

- 14b, 2Gsps, Self-Calibrating Current Steering IQDAC in samsung 8nm for 5G & WIFI6

- 14b, 4Gsps, Self-Calibrating Current Steering IQ DAC for 5G & WIFI6 in samsung 8nm

- WiFi6/BLE combo RFIP in 22nm

- Dual channel 12-bit, 640MS/s ADC IP for WIFI6 in TSMC 22nm

- Dual channel 12-bit, 2GS/s ADC for 5G & WIFI6 in Samsung 8nm