You are here:

eMMC 5.1 Host Controller

The eMMC 5.0 Host Controller IP is a highly integrated host controller IP solution. This Host Controller IP handles all of the timing and interface protocol requirements to access these media as well as processing the commands in hardware thereby scaling in both performance and access speeds. The IP supports connection to a single slot and performs multi-block writes and erases that lower access overhead. In addition, a host can utilize this IP to boot directly from an attached eMMC memory, thereby simplifying system initialization during power up. eMMC5.0 host interface is based on a standard 32-bit AXI bus which is used to transfer data and configure the IP.

查看 eMMC 5.1 Host Controller 详细介绍:

- 查看 eMMC 5.1 Host Controller 完整数据手册

- 联系 eMMC 5.1 Host Controller 供应商

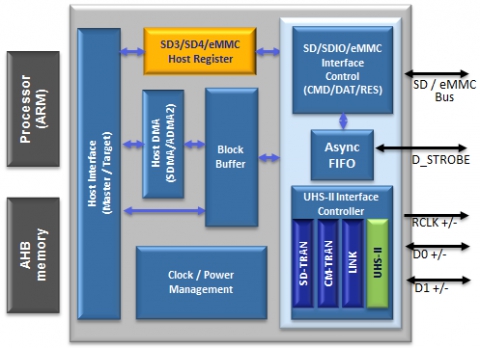

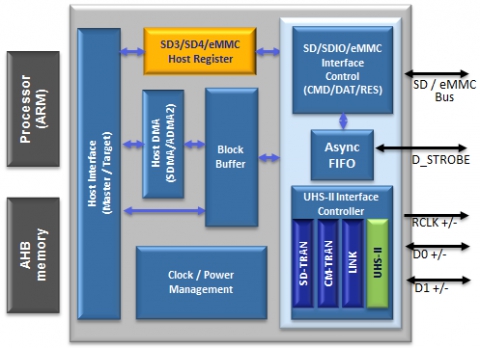

Block Diagram of the eMMC 5.1 Host Controller