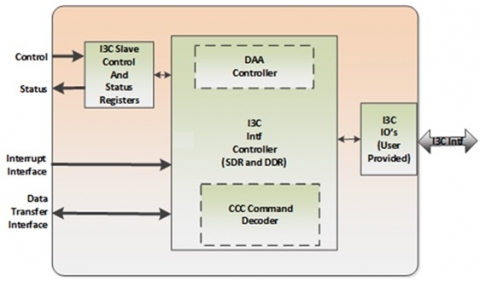

I3C Slave Controller

The I3C Slave controller is highly configurable (synthesis time) to provide an optimal solution based on the Device’s requirements. This include, acting as a legacy I2C device, Support for Dynamic Address Assignment, HDR (any of the three defined HDR Modes) and a configurable FIFO for data transfers. In addition, optional I3C slave functions like Interrupt generation, Hot-Join request generation and advanced slave with secondary master capabilities can be configured for more complex slaves. Also, the I3C Slave Controller IP provides direct signalling to connect to the IO Buffers (SCL and SDA). Please note that the User need to provide appropriate IO buffers to meet the I3C specification.

The I3C Slave controller implements support for legacy I2C Slave functionality, Open-drain and Push-pull operation of I3C Interface, and Dynamic Addressing support. The I3C Slave Controller supports the required SDR mode with Clock frequency of up to 12.5 MHz and optionally the any or all of the three HDR modes as defined by the I3C Specification. The included 16 byte FIFO (Configurable) is used to handle data transfers between IP and the Application.

查看 I3C Slave Controller 详细介绍:

- 查看 I3C Slave Controller 完整数据手册

- 联系 I3C Slave Controller 供应商

Block Diagram of the I3C Slave Controller