You are here:

I2C Slave Controller - Low Power, Low Noise Config of User Registers

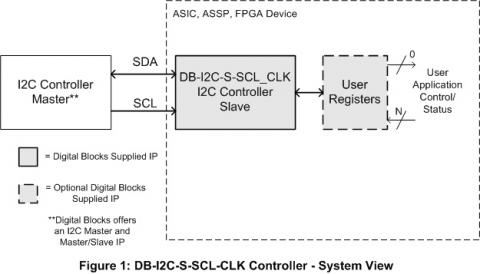

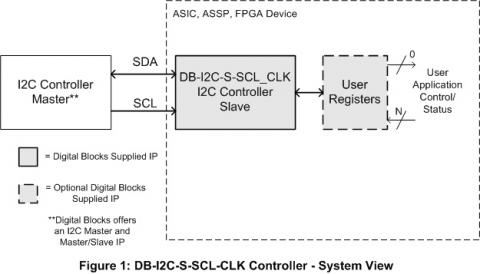

The DB-I2C-S-SCL-CLK is an I2C Slave Controller IP Core focused on low power, low noise ASIC / ASSP designs requiring the configuration & control of registers with no free running clock. The DB-I2C-S-SCL-CLK processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload to / from User Registers within an ASIC / ASSP / FPGA device.

The DB-I2C-S-SCL-CLK is a member of Digital Blocks DB-I2C Controller IP Core family, which includes I2C Master/Slave, I2C Master-only, and I2C Slave-only configurations.

The DB-I2C-S-SCL-CLK is a member of Digital Blocks DB-I2C Controller IP Core family, which includes I2C Master/Slave, I2C Master-only, and I2C Slave-only configurations.

查看 I2C Slave Controller - Low Power, Low Noise Config of User Registers 详细介绍:

- 查看 I2C Slave Controller - Low Power, Low Noise Config of User Registers 完整数据手册

- 联系 I2C Slave Controller - Low Power, Low Noise Config of User Registers 供应商

Block Diagram of the I2C Slave Controller - Low Power, Low Noise Config of User Registers

I2C Slave Controller IP

- I2C and SPI Master/Slave Controller

- I2C Master/Slave Controller Core IP

- I2C Master / Slave Controller w/FIFO (AHB & AHB-Lite Bus)

- I2C Master / Slave Controller w/FIFO (APB Bus)

- Hs-Mode I2C Controller - 3.4 Mbps, Master / Slave w/FIFO

- I2C Slave Controller w/FIFO (APB or AHB or AHB-Lite or AXI-Lite Bus)