2.5Gbps Per Lane MIPI-CSI2 Compliant Serial Video Transmitter

You are here:

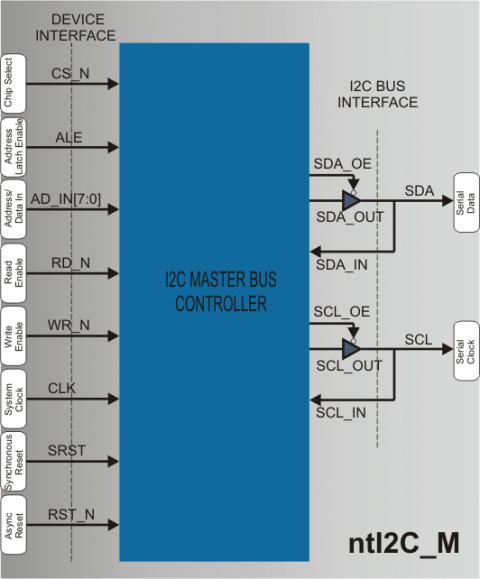

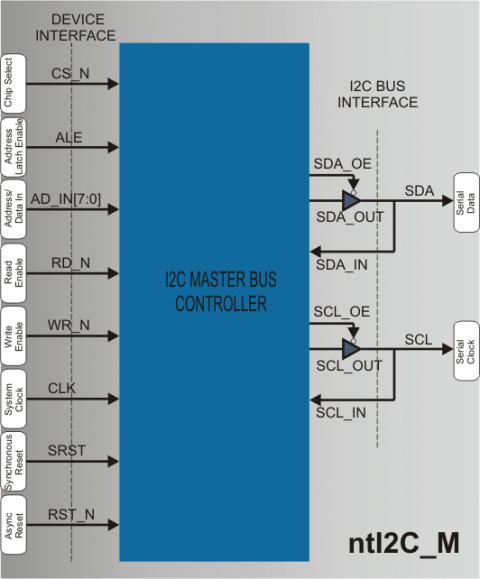

I2C Master Controller

The ntI2C_M is an I2C-bus multi-master interface controller and provides a cost-effective solution for a wide range of applications that require a low-cost serial communication channel. It provides a serial interface be-tween a device and an I2C-bus, where an external host processor is controlling the device via the I2C-bus and the I2C master interface unit. The I2C-bus communication protocol is ideal for applications where low power consumption and noise tolerance is of crucial impor-tance as well as in cases where low device interconnection overhead is strongly required. These features render the I2C-bus an ideal solu-tion for portable systems and battery-powered applications. The I2C standard is a multi-master bus that handles collision detection and arbitration thus preventing data corruption if two or more masters attempt to control the bus simultaneously. Practically the I2C-bus interface is a parallel to serial and serial to parallel converter. The serial data received from I2C-bus is converted to parallel for the CPU device. The parallel data received from the CPU or any other target device is converted to serial form for transmission on the I2C-bus. The ntI2C_M core is available in VHDL and is synthesizable to any FPGA or ASIC technology. The core can be easily customized for spe-cific customer needs and is provided with test-benches and full documentation.

查看 I2C Master Controller 详细介绍:

- 查看 I2C Master Controller 完整数据手册

- 联系 I2C Master Controller 供应商

Block Diagram of the I2C Master Controller