You are here:

Home Plug Green PHY MAC Layer TX/RX

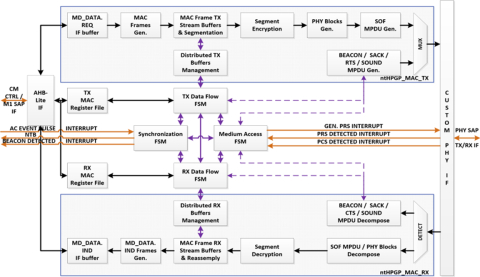

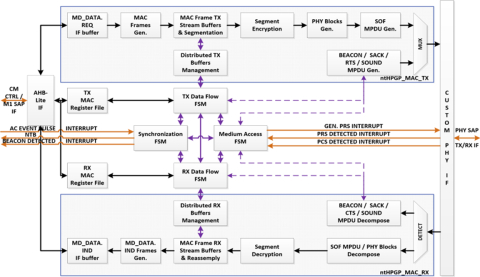

ntHPGP_MAC IP core implements “Connectionless CSMA-Only Level-0 CCo“ MAC Layer functionality with Passive Coordination, as detailed in Chapter 5 of “HomePlug Green PHY 1.1.1” (HPGP) specification document.

The MAC Layer is positioned in the middle of the HPGP Protocol Layer Architecture and it manages communication and transactions between all surrounding HPGP Layers.

Namely it is connected to the Connection Manager (CCo) via the Control SAP IF ports, to the Convergence Layer via the M1 SAP IF ports and to the PHY Layer via the MAC-PHY SAP IP ports.

All these 3 Service Access Points (SAP) are loosely defined in the specification document. The MAC is also tasked to determine the correct time position of transmission, format data frames into fixed length entities and ensure

timely and error-free delivery.

ntHPGP_MAC IP defines customizable interfaces and optional interrupt ports for all 3 SAP ports and implements specific detailed packet and timing protocols for the communication with all adjacent HPGP Protocol layers.

The implementation is further partitioned to the Control Plane and the Data Plane. The Control plane is implemented with a number of coordinated and distributed FSM controllers, each managing a standalone MAC Layer system task.

A set of Synchronization FSMs manage the AC Line Synchronization, the Network Time Base (NTB) Synchronization and the Beacon Period Tracking. A set of Medium Access FSMs both implement and manage the CSMA/CA medium access protocol, implement the Virtual Carrier Sense (VCS) mechanism and ultimately cooperate with Synchronization FSMs to indicate appropriate Transmit and Receive periods to the system.

The TX and RX data-flow FSMs make timely decisions regarding the types of MPDU frames that need to be transmitted or effectively detect the received MPDU frames.

The Data plane is implemented with the TX and RX data-path IPs. The TX IP accepts MD_DATA.REQ primitives and ultimately converts MSDU/MME payload to SOF MPDU Frames.

This procedure involves conversion of MSDU/MME to MAC Frames, segregation of MAC Frames to MAC Frame Streams, segmentation, encryption, formation of Payload Blocks and finally SOF MPDU Frames generation.

The inverse procedure is implemented by the RX IP, which accepts MDPU Frames and converts them back to MD_DATA.IND primitives.

The MAC Layer is positioned in the middle of the HPGP Protocol Layer Architecture and it manages communication and transactions between all surrounding HPGP Layers.

Namely it is connected to the Connection Manager (CCo) via the Control SAP IF ports, to the Convergence Layer via the M1 SAP IF ports and to the PHY Layer via the MAC-PHY SAP IP ports.

All these 3 Service Access Points (SAP) are loosely defined in the specification document. The MAC is also tasked to determine the correct time position of transmission, format data frames into fixed length entities and ensure

timely and error-free delivery.

ntHPGP_MAC IP defines customizable interfaces and optional interrupt ports for all 3 SAP ports and implements specific detailed packet and timing protocols for the communication with all adjacent HPGP Protocol layers.

The implementation is further partitioned to the Control Plane and the Data Plane. The Control plane is implemented with a number of coordinated and distributed FSM controllers, each managing a standalone MAC Layer system task.

A set of Synchronization FSMs manage the AC Line Synchronization, the Network Time Base (NTB) Synchronization and the Beacon Period Tracking. A set of Medium Access FSMs both implement and manage the CSMA/CA medium access protocol, implement the Virtual Carrier Sense (VCS) mechanism and ultimately cooperate with Synchronization FSMs to indicate appropriate Transmit and Receive periods to the system.

The TX and RX data-flow FSMs make timely decisions regarding the types of MPDU frames that need to be transmitted or effectively detect the received MPDU frames.

The Data plane is implemented with the TX and RX data-path IPs. The TX IP accepts MD_DATA.REQ primitives and ultimately converts MSDU/MME payload to SOF MPDU Frames.

This procedure involves conversion of MSDU/MME to MAC Frames, segregation of MAC Frames to MAC Frame Streams, segmentation, encryption, formation of Payload Blocks and finally SOF MPDU Frames generation.

The inverse procedure is implemented by the RX IP, which accepts MDPU Frames and converts them back to MD_DATA.IND primitives.

查看 Home Plug Green PHY MAC Layer TX/RX 详细介绍:

- 查看 Home Plug Green PHY MAC Layer TX/RX 完整数据手册

- 联系 Home Plug Green PHY MAC Layer TX/RX 供应商

Block Diagram of the Home Plug Green PHY MAC Layer TX/RX