You are here:

Hardware RTP Stack for JPEG Stream Encapsulation

Implements a Real Time Transport Protocol (RTP) hardware stack that encapsulates JPEG streams to RTP packets compliant with RFC 2435.

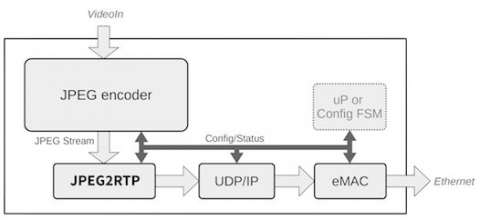

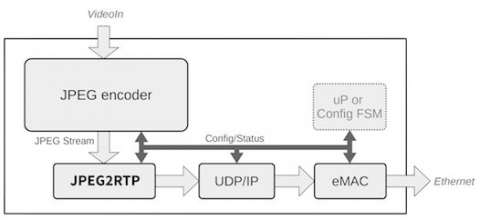

The JPEG2RTP can be directly connected to the output of a JPEG encoder to output RTP packets, which can subsequently be forwarded for UDP/IP or TCP/IP encapsulation. The hardware stack produces complete RTP packets, without the need for any host-processor assistance. Along with CAST’s UDP/IP hardware stack, the JPEG2RTP core is ideal for offloading the demanding task of RTP/UDP/IP encapsulation from a host processor, and enables JPEG video streaming even in processor-less SoC designs.

The core is easy to integrate in systems with or without a host processor. JPEG stream and RTP packet data are input/output via dedicated streaming-capable AMBA® AXI4®-Stream or Altera® Avalon®-ST interfaces, enabling direct connection to hardware video encoders and hardware stacks for UDP or TCP. Status and control registers are accessible by AXI4-Lite or Avalon-MM interface.

The JPEG2RTP core is available in RTL source or as a targeted FPGA netlist. Platforms integrating the core along with JPEG encoder, UDP/IP, and eMAC cores, are available from CAST, and can enable rapid development of video over IP systems.

The JPEG2RTP can be directly connected to the output of a JPEG encoder to output RTP packets, which can subsequently be forwarded for UDP/IP or TCP/IP encapsulation. The hardware stack produces complete RTP packets, without the need for any host-processor assistance. Along with CAST’s UDP/IP hardware stack, the JPEG2RTP core is ideal for offloading the demanding task of RTP/UDP/IP encapsulation from a host processor, and enables JPEG video streaming even in processor-less SoC designs.

The core is easy to integrate in systems with or without a host processor. JPEG stream and RTP packet data are input/output via dedicated streaming-capable AMBA® AXI4®-Stream or Altera® Avalon®-ST interfaces, enabling direct connection to hardware video encoders and hardware stacks for UDP or TCP. Status and control registers are accessible by AXI4-Lite or Avalon-MM interface.

The JPEG2RTP core is available in RTL source or as a targeted FPGA netlist. Platforms integrating the core along with JPEG encoder, UDP/IP, and eMAC cores, are available from CAST, and can enable rapid development of video over IP systems.

查看 Hardware RTP Stack for JPEG Stream Encapsulation 详细介绍:

- 查看 Hardware RTP Stack for JPEG Stream Encapsulation 完整数据手册

- 联系 Hardware RTP Stack for JPEG Stream Encapsulation 供应商

Block Diagram of the Hardware RTP Stack for JPEG Stream Encapsulation

RTP Stack for JPEG IP

- RTP / UDP / IP Hardware Stack for Raw, Uncompressed RGB/YUV Video Streams

- RTP / UDP / IP Hardware Stack for H.264/H.265 NAL Video Streams Packet Processing

- Hardware RTP Stack for H.264 Stream Encapsulation

- Motion JPEG Over IP - HD Video Encoder Subsystem

- Hardware RTP Stack for H.264 Stream Decapsulation

- RTP packetizer IP-cores for JPEG XS compressed video encapsulation over ST2110-22