Gigabit Ethernet Media Access Controller

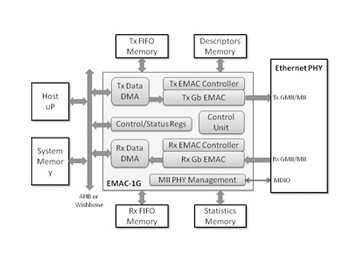

A host processor can control the operation of the core via a slave interface that provides access to its control and status registers. The EMAC-1G features two master ports for data transfers, one for transmit and one for receive. The two DMA engines use buffer descriptors to automatically transfer data from local FIFOs to an external shared memory. The core supports 32-bit AMBA/AHB or Wishbone SoC buses; other bus interfaces are available on request.

Integration with an Ethernet PHY is straightforward, as the controller core supports the Media Independent Interface (MII) and the Gigabit Media Independent Interface (GMII) physical layer interface standards.

The EMAC-1G is production proven in ASIC and FPGA technologies.

查看 Gigabit Ethernet Media Access Controller 详细介绍:

- 查看 Gigabit Ethernet Media Access Controller 完整数据手册

- 联系 Gigabit Ethernet Media Access Controller 供应商

Block Diagram of the Gigabit Ethernet Media Access Controller

mac IP

- The Synopsys 1.6T Ethernet MAC IP is based on IEEE 802.3-2018 spec for 400Gbps, 800Gbps & 1.6Tbps Ethernet applications

- Synopsys 1.6T Ethernet MAC IP

- Turnkey UWB MAC and PHY platform IP, for FiRa 2.0, CCC Digital Key 3.0, and Radar

- Ceva-Waves 802.11be (Wi-Fi 7) 2x2 MAC & Modem AP

- 100G Ethernet MAC/RS

- 10G/25GBASE-R MAC Core