You are here:

Floating-point Adder

High-speed fully pipelined 32-bit floating-point adder/subtracter based on the IEEE 754 standard. Results have a latency of 5 clock cycles.

Ideal for floating-point pipelines, arithmetic units and processors.

Ideal for floating-point pipelines, arithmetic units and processors.

查看 Floating-point Adder 详细介绍:

- 查看 Floating-point Adder 完整数据手册

- 联系 Floating-point Adder 供应商

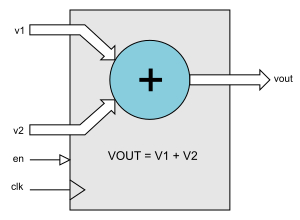

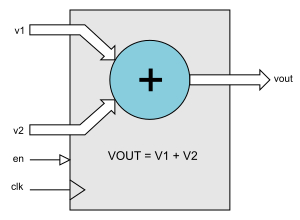

Block Diagram of the Floating-point Adder

IEEE 754 IP

- IEEE 754 Floating Point Coprocessor

- Single precision floating-point fast speed parametrized multi operands adder

- Single precision floating-point 2 cycle's multiplier

- Floating-point (IEEE 754) IP based on Arria 10 and Stratix 10 FPGAs

- Single precision, IEEE 754, floating point adder

- Single precision, IEEE 754, floating point multiplier