You are here:

DO-254 SDRAM Controller

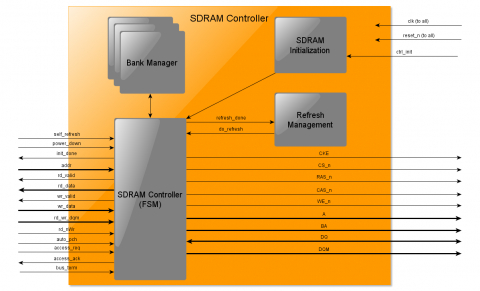

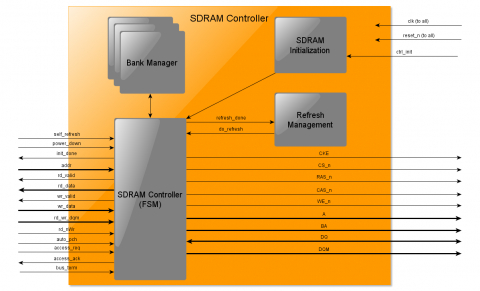

The SDRAM Controller implements a controller for Single Data Rate Syncrhonous Dynamic Random Access Memory (SDR SDRAM) decives as specified in the JEDEC Standard No. 21-C Page 3.11.5.1 Release 12.

Single Data Rate SDRAM can accept one command and transfer one word of data per clock cycle. Typical clock frequencies are 100 and 133 MHz. Chips are made with a variety of data bus sizes.

SDRAM is still being manufactured and the maturity of this technology makes it ideal for systems that need performance at a low cost.

The SDRAM Controller has been developed to DAL A according to the DO-254. For lower DAL levels reduced documentation sets are available. The core is also available as a netlist for DAL D or projects not needing the full RTL source.

Single Data Rate SDRAM can accept one command and transfer one word of data per clock cycle. Typical clock frequencies are 100 and 133 MHz. Chips are made with a variety of data bus sizes.

SDRAM is still being manufactured and the maturity of this technology makes it ideal for systems that need performance at a low cost.

The SDRAM Controller has been developed to DAL A according to the DO-254. For lower DAL levels reduced documentation sets are available. The core is also available as a netlist for DAL D or projects not needing the full RTL source.

查看 DO-254 SDRAM Controller 详细介绍:

- 查看 DO-254 SDRAM Controller 完整数据手册

- 联系 DO-254 SDRAM Controller 供应商

Block Diagram of the DO-254 SDRAM Controller