You are here:

Display Port v1.4 Tx PHY 和控制器 IP,在 TSMC 12FFC 中经过硅验证

12FFC中的DisplayPort v1.4 Tx PHY IP是一种现代化技术,旨在集成到各种设备的芯片设计中,包括图形卡、显示器和笔记本电脑。利用12nm FinFET Compact工艺技术,该IP在功率效率和性能之间取得了平衡,使其成为实现DisplayPort 1.4功能的理想解决方案。使用该DisplayPort 1.4 Tx PHY IP,设备制造商可以在其产品中实现高质量视频和音频信号的无缝传输。这种集成增强了用户的视觉体验,提供了DisplayPort 1.4支持的高级功能和高速数据传输功能。该发射机PHY支持范围广泛的比特率,从1.62Gbps(RBR)到5.4Gbps(HBR2),确保了现代显示技术中的高效数据传输。它包括集成功能,如具有共模偏置的100欧姆终端电阻器,这提高了信号的完整性,并且该发射机PHY包含具有可调强度的集成均衡器,允许在长电缆长度或具有挑战性的环境中进行信号优化。IP还提供可配置的模拟特性,包括CDR带宽、均衡器强度、终端电阻、BGR电压和调节器电压。这种灵活性使定制能够满足特定的要求,并增强了与不同系统配置的兼容性。12FFC中的DisplayPort 1.4 Tx PHY IP在推进显示技术和促进各个行业未来设备的发展方面发挥着至关重要的作用。它与芯片设计的集成使设备制造商能够向用户提供增强的视觉体验,同时保持高效的数据传输能力。

查看 Display Port v1.4 Tx PHY 和控制器 IP,在 TSMC 12FFC 中经过硅验证 详细介绍:

- 查看 Display Port v1.4 Tx PHY 和控制器 IP,在 TSMC 12FFC 中经过硅验证 完整数据手册

- 联系 Display Port v1.4 Tx PHY 和控制器 IP,在 TSMC 12FFC 中经过硅验证 供应商

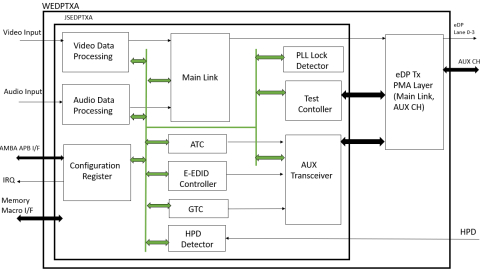

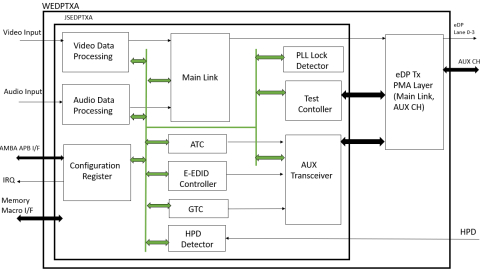

Block Diagram of the Display Port v1.4 Tx PHY 和控制器 IP,在 TSMC 12FFC 中经过硅验证

Display Port v1.4 Tx PHY IP Core IP

- Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in TSMC 28HPC+

- Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in UMC 28HPC

- Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in UMC 40SP

- Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in TSMC 40LP

- Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in UMC 55SP

- Display Port 1.2 Tx PHY & Controller IP (Silicon Proven in STMicro 28FDSOI)