You are here:

Compact, efficient 64-bit RISC-V processor with 5-stage pipeline

The H50 is an entry level, compact, efficient 64-bit embedded RISC-V processor aimed at embedded systems requiring a large address space. The core has a 5-stage pipeline and is offered in two versions.

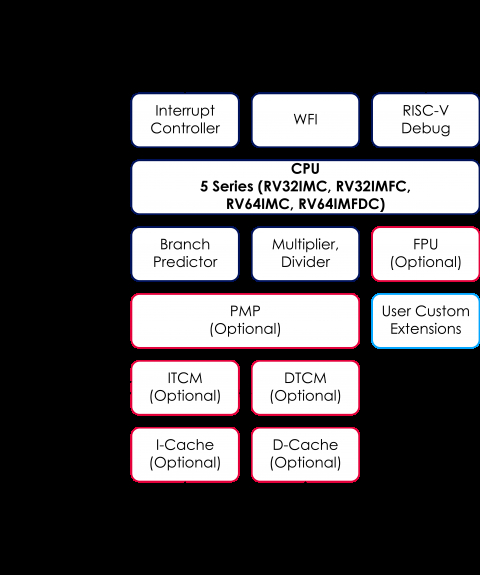

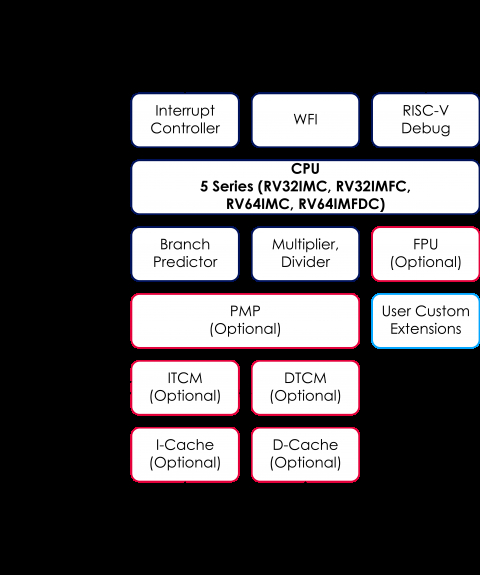

The core includes optional L1 data and instruction caches, optional instruction and data TCM, optional 8 or 16 PMP regions, an interrupt controller and RISC-V Debug module optionally with PC trace.

Like with all Codasip RISC-V cores, it is possible to create custom instructions using Codasip Studio to extend the H50 and to generate corresponding hardware and software development kits.

The core includes optional L1 data and instruction caches, optional instruction and data TCM, optional 8 or 16 PMP regions, an interrupt controller and RISC-V Debug module optionally with PC trace.

Like with all Codasip RISC-V cores, it is possible to create custom instructions using Codasip Studio to extend the H50 and to generate corresponding hardware and software development kits.

查看 Compact, efficient 64-bit RISC-V processor with 5-stage pipeline 详细介绍:

- 查看 Compact, efficient 64-bit RISC-V processor with 5-stage pipeline 完整数据手册

- 联系 Compact, efficient 64-bit RISC-V processor with 5-stage pipeline 供应商

Block Diagram of the Compact, efficient 64-bit RISC-V processor with 5-stage pipeline

RISC-V IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- ARC-V RHX-100 dual-issue, 32-bit single-core RISC-V processor for real-time applications

- 32-bit Embedded RISC-V Functional Safety Processor