You are here:

CCSDS (8160,7136) LDPC Decoder

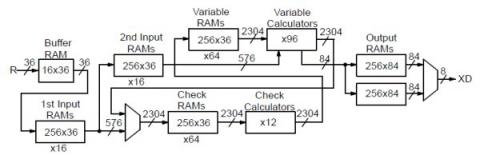

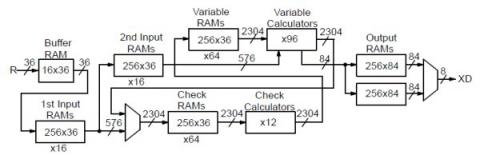

The LDPC Decoder is a fully compatible CCSDS rate 223/255 (8160,7136) LDPC [1] error control decoder. A regular quasic–cyclic LDPC code with 511x511 square circulants with weight 2 in the parity check matrix is used. There are 2x16 circulants, resulting in a check node degree of 32 and a variable node degree of 4.

In each clock cycle, 12 check nodes (12x32 = 384 messages) or 96 variable nodes (96x4 = 384 messages) are fully decoded. Each iteration requires 86 clock cycles to calculate the check or variable messages plus a 7 clock cycle pipeline delay. The scaled min–sum iterative decoding algorithm [2] is used.

The LDPC decoder can achieve up to 1650 Mbit/s with 10 iterations using a 216 MHz internal clock. Optional early stopping allows the decoder to reduce power consumption with little degradation in performance.

The decoder contains two sets of message memories so that check and variable calculations can be performed in parallel. Two input memories are used to buffer the input data.

In each clock cycle, 12 check nodes (12x32 = 384 messages) or 96 variable nodes (96x4 = 384 messages) are fully decoded. Each iteration requires 86 clock cycles to calculate the check or variable messages plus a 7 clock cycle pipeline delay. The scaled min–sum iterative decoding algorithm [2] is used.

The LDPC decoder can achieve up to 1650 Mbit/s with 10 iterations using a 216 MHz internal clock. Optional early stopping allows the decoder to reduce power consumption with little degradation in performance.

The decoder contains two sets of message memories so that check and variable calculations can be performed in parallel. Two input memories are used to buffer the input data.

查看 CCSDS (8160,7136) LDPC Decoder 详细介绍:

- 查看 CCSDS (8160,7136) LDPC Decoder 完整数据手册

- 联系 CCSDS (8160,7136) LDPC Decoder 供应商

Block Diagram of the CCSDS (8160,7136) LDPC Decoder