卷积编码器

莱迪思的卷积编码器IP核是一个可配置参数的IP核,可用于连续或突发输入数据流的编码。该IP核支持各种码率、约束长度并支持打孔算法。IP核可以在连续或块模式下工作,由通道决定。在块模式下,支持Tail Biting或Zero Flushing卷积码。所有可配置的参数,包括工作模式、终止模式、生成多项式、码率、打孔模式(puncture pattern)都可以由用户定义,以满足其应用需求。码率和打孔模式也可以通过输入端口进行动态更改,为IP的使用提供更大的灵活性。莱迪思卷积编码器IP核符合多种使用卷积编码的网络和无线标准。

查看 卷积编码器 详细介绍:

- 查看 卷积编码器 完整数据手册

- 联系 卷积编码器 供应商

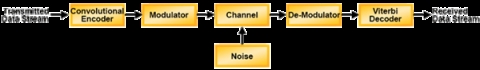

Block Diagram of the 卷积编码器

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software