You are here:

Bandgap Voltage / Current Reference SMIC

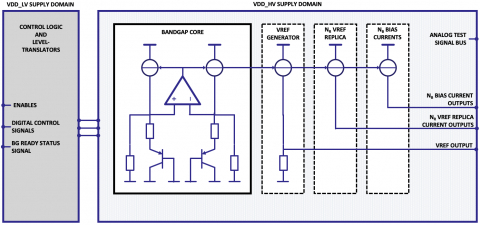

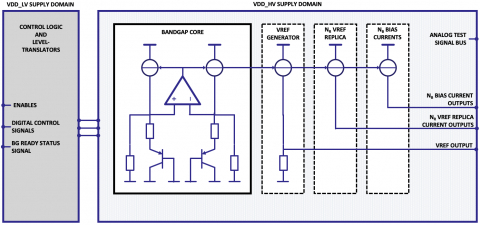

The agileBandGapGP consists of a bandgap reference core together with a bandgap reference voltage generator (VREF), VREF replica current generators and bias current generators. The number of output bias currents can be specified up to a maximum of 16 configurable outputs. Agile Analog designs are based on tried and tested architectures to ensure reliability and functionality. Our design methodology is programmatic, systematic and repeatable, leading to analog IP that is more verifiable, more robust and more reliable.

查看 Bandgap Voltage / Current Reference SMIC 详细介绍:

- 查看 Bandgap Voltage / Current Reference SMIC 完整数据手册

- 联系 Bandgap Voltage / Current Reference SMIC 供应商

Block Diagram of the Bandgap Voltage / Current Reference SMIC

LDO IP

- LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output

- LDO Voltage Regulator, 250 mA, Adjustable 0.45 V to 0.9 V Output

- Analog Front End: 2x 12-bit 4 GSPS IQ ADCs, 2x 12-bit 8GSPS IQ DACs, bandgap, temp sensor, PLL, 4 x LDO

- LDO Linear Voltage Regulator

- Ultra-low quiescent LDO voltage regulator in TSMC 22ULL

- Capless 1.8V output LDO with 2.0-3.6V input range - 0.18 EF