You are here:

AHB Quad SPI Controller with Execute in Place

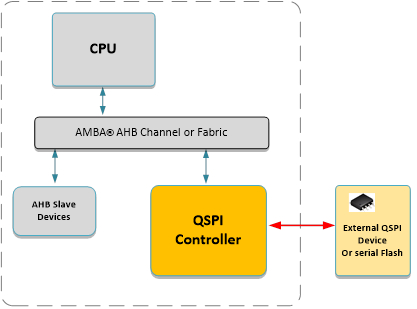

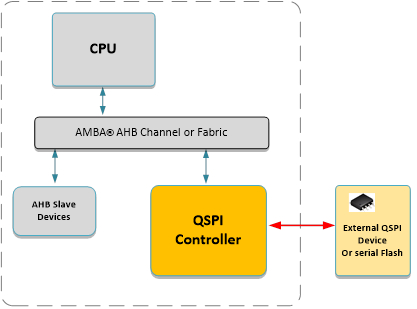

The Quad Serial Peripheral Interface (OSPI) core is a serial data link (SPI) master which controls an external serial FLASH device.

Reading and writing the core is done on the AMBA® AHB bus interface. The data is then serialized and then transmitted, either LSB or MSB first, using the standard 4-wire SPI bus interface or the extended Dual, r Quad Bus modes.

The OSPI is compatible with various industry-standard DMA controllers. DMA operation in the OSPI can be enabled to assist a DMA controller in the loading (writing) of the transmit FIFO, and the unloading (reading) of the receive FIFO.

The Execute in Place (XIP) Mode allows an AHB Master to directly read the contents of any of several industry-standard FLASH devices (such as Winbond, Macronix, Spansion and Micron devices) simply by reading from the address space of the QSPI Controller.

Reading and writing the core is done on the AMBA® AHB bus interface. The data is then serialized and then transmitted, either LSB or MSB first, using the standard 4-wire SPI bus interface or the extended Dual, r Quad Bus modes.

The OSPI is compatible with various industry-standard DMA controllers. DMA operation in the OSPI can be enabled to assist a DMA controller in the loading (writing) of the transmit FIFO, and the unloading (reading) of the receive FIFO.

The Execute in Place (XIP) Mode allows an AHB Master to directly read the contents of any of several industry-standard FLASH devices (such as Winbond, Macronix, Spansion and Micron devices) simply by reading from the address space of the QSPI Controller.

查看 AHB Quad SPI Controller with Execute in Place 详细介绍:

- 查看 AHB Quad SPI Controller with Execute in Place 完整数据手册

- 联系 AHB Quad SPI Controller with Execute in Place 供应商

Block Diagram of the AHB Quad SPI Controller with Execute in Place

QSPI IP

- AXI QSPI with Execute in Place

- Specialized 1.2V to 3.3V Fail-Safe GPIO and 3.3V I2C Open-Drain, SPI in TSMC 110nm

- Specialized 1.2V to 3.3V Fail-Safe GPIO and 3.3V I2C Open-Drain in 110nm

- Flipchip 5V Fail-Safe GPIO, 5V GPIO, 5V GPI and I2C Compliant 5V ODIO

- Quad SPI Master IP

- QSPI FLASH Controller – XIP functionality (SINGLE, DUAL and QUAD SPI Bus Controller with Double Data Rate support)