You are here:

64-bit Multiprocessor with Level-2 Cache-Coherence

AndesCore™ AX45MP 64-bit multicore CPU IP is an 8-stage superscalar processor based on AndeStar™ V5 architecture. It supports RISC-V standard “G (IMAC-FD)” extensions, “C” 16-bit compression instructions, DSP/SIMD ‘P’ extension (draft), user-level interrupt ‘N’ extension, and Andes performance/ functionality enhancements for faster memory accesses and branch handling, plus Andes Custom Extension™ (ACE) to add user-defined instructions. It features MMU for Linux based applications, branch prediction for efficient branch execution, level-1 instruction/data caches and local memories for low-latency accesses.

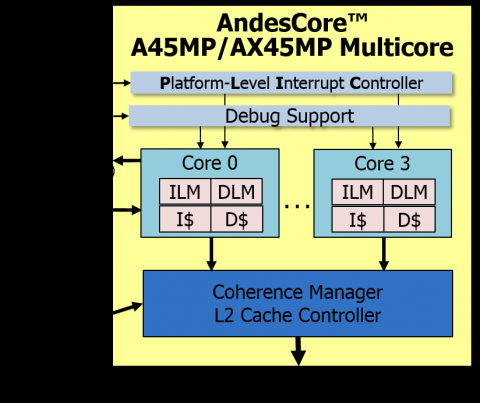

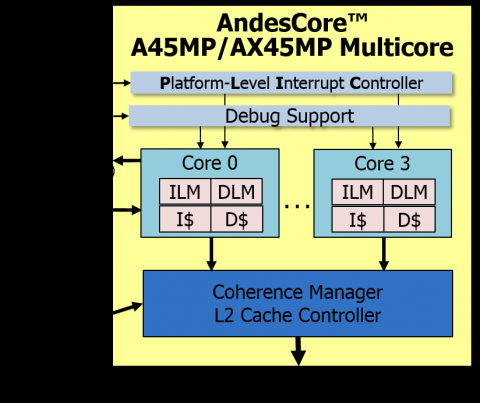

The AX45MP symmetric multiprocessor supports up to 4 cores and a level-2 cache controller with instruction and data prefetch. Coherence manger implements MESI protocol to manage level-1 cache coherence, including I/O coherence for cacheless bus masters. Other AX45MP features include ECC for level-1/2 memory soft error protection, Platform-Level Interrupt Controller (PLIC) with enhancements for vectored dispatch and priority-based preemption, CoDense™, StackSafe™ for software quality improvement, and QuickNap™, PowerBrake, and WFI for power management.

The AX45MP symmetric multiprocessor supports up to 4 cores and a level-2 cache controller with instruction and data prefetch. Coherence manger implements MESI protocol to manage level-1 cache coherence, including I/O coherence for cacheless bus masters. Other AX45MP features include ECC for level-1/2 memory soft error protection, Platform-Level Interrupt Controller (PLIC) with enhancements for vectored dispatch and priority-based preemption, CoDense™, StackSafe™ for software quality improvement, and QuickNap™, PowerBrake, and WFI for power management.

查看 64-bit Multiprocessor with Level-2 Cache-Coherence 详细介绍:

- 查看 64-bit Multiprocessor with Level-2 Cache-Coherence 完整数据手册

- 联系 64-bit Multiprocessor with Level-2 Cache-Coherence 供应商

Block Diagram of the 64-bit Multiprocessor with Level-2 Cache-Coherence

RISC-V; superscalar;dual-issue;8-stage pipeline;microprocessor;DSP IP

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP (DSP)

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

- 64-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

- 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

- 64-bit RISC-V Multicore Processor with 1024-bit Vector Extension

- Compact, Secure and Performance Efficiency 32-bit RISC-V Core