You are here:

2.5Gbps以太网PCS IP核

莱迪思2.5 Gbps以太网PCS IP核实现了IEEE 802.3z(1000BaseX)规范中物理编码子层(PCS)的状态机功能。需要注意的是,IEEE规范说明的是工作速率为1Gbps的PCS。因此,根据IEEE规范,这个2.5G PCS IP核并不是标准的。

不符合标准的主要有数据速率(2.5 Gbps而不是1 Gbps)和GMII数据总线宽度(16位而不是8位)。

这个PCS IP核是专门开发用于与莱迪思2.5 Gbps MAC IP核一起工作的。莱迪思2.5G PCS和MAC IP核100%兼容,并可以用来开发一个完整的PHY/MAC以太网数据通道,工作速率为2.5 Gbps。

本文档介绍了2.5 Gbps以太网PCS IP核的工作,并提供使用莱迪思IPexpress™工具生成、实例化、综合和仿真IP核的指导说明。

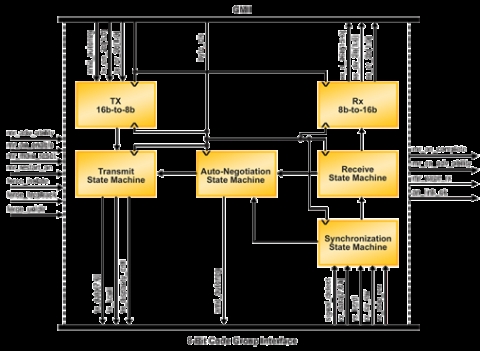

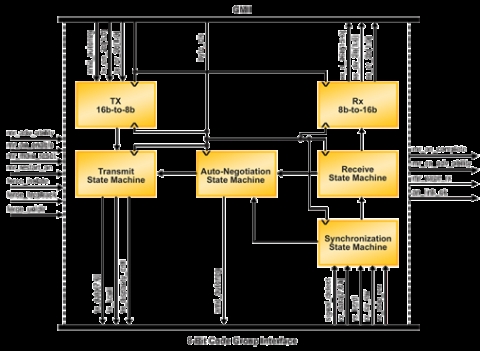

根据IEEE 802.3z规范,2.5 Gbps以太网PCS IP核在发送和接收时,将GMII帧转换成8位代码组,并与连接伙伴进行自动协商。

不符合标准的主要有数据速率(2.5 Gbps而不是1 Gbps)和GMII数据总线宽度(16位而不是8位)。

这个PCS IP核是专门开发用于与莱迪思2.5 Gbps MAC IP核一起工作的。莱迪思2.5G PCS和MAC IP核100%兼容,并可以用来开发一个完整的PHY/MAC以太网数据通道,工作速率为2.5 Gbps。

本文档介绍了2.5 Gbps以太网PCS IP核的工作,并提供使用莱迪思IPexpress™工具生成、实例化、综合和仿真IP核的指导说明。

根据IEEE 802.3z规范,2.5 Gbps以太网PCS IP核在发送和接收时,将GMII帧转换成8位代码组,并与连接伙伴进行自动协商。

查看 2.5Gbps以太网PCS IP核 详细介绍:

- 查看 2.5Gbps以太网PCS IP核 完整数据手册

- 联系 2.5Gbps以太网PCS IP核 供应商

Block Diagram of the 2.5Gbps以太网PCS IP核

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software