2.5Gbps Per Lane MIPI-CSI2 Compliant Serial Video Transmitter

You are here:

16-bt Sigma Delta ADC - Globalfoundries 130LP

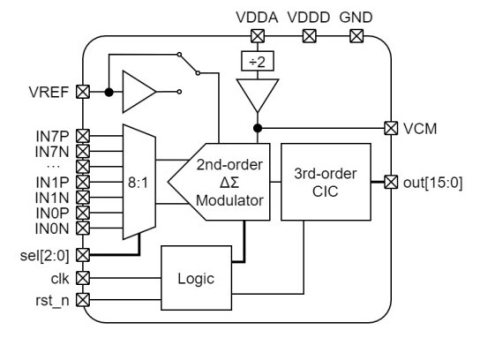

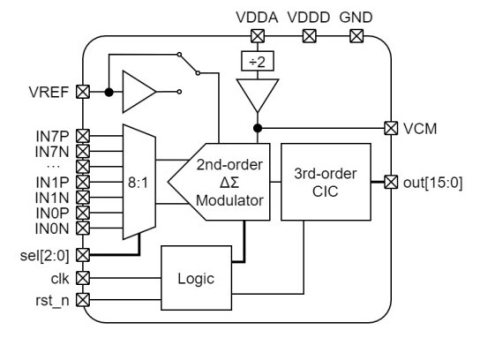

The IP is a 16-bit, delta-sigma (ΔΣ), analog-to-digital converter (ADC). It comprises of a second-order discrete-time modulator followed by a third-order CIC decimation filter with programmable output rate.

Two operation modes are supported: single differential input (free-running mode) or multiplexing of up to 8 differential channels (incremental mode).

The IP integrates a reference voltage buffer and common-mode generation. It requires an external clock of 8 MHz for 4 kSps data rate. A slower clock may be used to reduce power consumption.

The modulator area is 322 x 276 µm. It consumes 87 µA from a 1.2 V or 1.5 V supply. The decimation filter is synthesised to 898 cells, which take roughly 0.02 mm2.

This IP is implemented on GF130LP CMOS process using 8 metal layers and baseline mask set (i.e., no MIM capacitors or thin-film resistors). Please get in touch to enquire about migration to other processes.

Two operation modes are supported: single differential input (free-running mode) or multiplexing of up to 8 differential channels (incremental mode).

The IP integrates a reference voltage buffer and common-mode generation. It requires an external clock of 8 MHz for 4 kSps data rate. A slower clock may be used to reduce power consumption.

The modulator area is 322 x 276 µm. It consumes 87 µA from a 1.2 V or 1.5 V supply. The decimation filter is synthesised to 898 cells, which take roughly 0.02 mm2.

This IP is implemented on GF130LP CMOS process using 8 metal layers and baseline mask set (i.e., no MIM capacitors or thin-film resistors). Please get in touch to enquire about migration to other processes.

查看 16-bit Sigma Delta ADC 详细介绍:

- 查看 16-bit Sigma Delta ADC 完整数据手册

- 联系 16-bit Sigma Delta ADC 供应商

Block Diagram of the 16-bit Sigma Delta ADC

16-bit Sigma Delta ADC IP

- 16-Bit Sigma-Delta CODEC (ADC & DAC) with headset, handset and 400mW Speaker Amplifier, Dongbu 0.11um

- 16bit 3Msps Sigma Delta ADC in 130nm~22nm

- 16bit 100Ksps Sigma Delta ADC in 130nm~22nm

- Extended Range Incremental Sigma Delta ADC

- 16 Bit Sigma Delta AD Converter

- 16-Bit 90dB SNR 8~48KHz stereo ADC with FM/MIC inputs, TSMC0.18um