You are here:

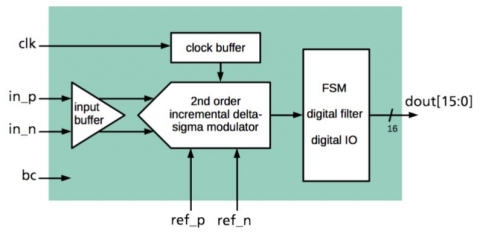

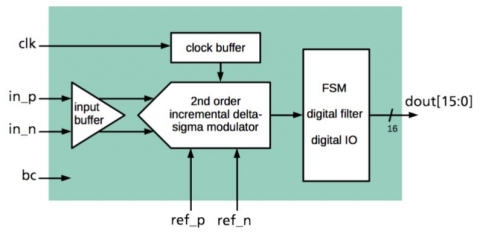

16 Bit 10 kS/s Incremental Delta - Sigma ADC

On the one hand, incremental delta-sigma modulators are able to convert DC and multiplexed input signals as known from Nyquist ADCs. On the other hand, using internal oversampling and noise shaping provides high linearity as known from delta-sigma ADCs.

This fully differential ADC is designed to convert full swing (-1V to +1 V) input signals as well as unipolar input signals (0V to + 1V), each with 16 bits resolution.

Low-frequency noise reduction is provided using chopper-modulation.

The embedded power down mode provides a linear relation between power consumption and conversion rate of the ADC. Scaling between power consumption, conversion rate and resolution can be achieved due to the selectable

number of conversion cycles.

The analog ADC frontend can also be used in combination with a custom digital filter for classical delta-sigma operation.

The ADC is silicon evaluated using the AMS H35 process. Measurement results and samples are available.

Fraunhofer IIS provides a detailed documentation and

support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

This fully differential ADC is designed to convert full swing (-1V to +1 V) input signals as well as unipolar input signals (0V to + 1V), each with 16 bits resolution.

Low-frequency noise reduction is provided using chopper-modulation.

The embedded power down mode provides a linear relation between power consumption and conversion rate of the ADC. Scaling between power consumption, conversion rate and resolution can be achieved due to the selectable

number of conversion cycles.

The analog ADC frontend can also be used in combination with a custom digital filter for classical delta-sigma operation.

The ADC is silicon evaluated using the AMS H35 process. Measurement results and samples are available.

Fraunhofer IIS provides a detailed documentation and

support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

查看 16 Bit 10 kS/s Incremental Delta - Sigma ADC 详细介绍:

- 查看 16 Bit 10 kS/s Incremental Delta - Sigma ADC 完整数据手册

- 联系 16 Bit 10 kS/s Incremental Delta - Sigma ADC 供应商

Block Diagram of the 16 Bit 10 kS/s Incremental Delta - Sigma ADC