xSPI Master IP | NOR IP

The xSPI master IP supports the xSPI JESD251 standard from a standard AXI4 slave interface, and also features backwards compatibility support for Octal SPI, QSPI, DSPI, and SPI interfaces. Also supports JEDEC SFDP Standard. It is designed so that a user design may immediately access memory from the xSPI device in SPI mode, or alternatively issue a command to switch to any other mode. Additionally, a DMA command may be issued to copy memory from the xSPI device to anywhere else on the bus.

查看 xSPI Master IP | NOR IP 详细介绍:

- 查看 xSPI Master IP | NOR IP 完整数据手册

- 联系 xSPI Master IP | NOR IP 供应商

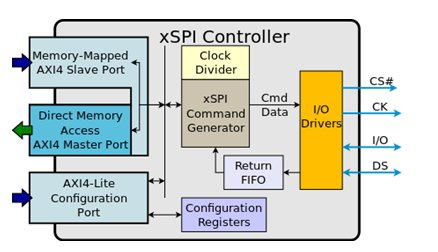

Block Diagram of the xSPI Master IP | NOR IP

Video Demo of the xSPI Master IP | NOR IP

Arasan Chip Systems, a leading provider of IP for Mobile Storage Standards, presents its JEDEC JESD251C Compliant xSPI IP, a superset of its Octal SPI IP, QSPI IP and PSRAM IP in addition to xSPI providing access to any NOR Flash Device. Arasan's Total xSPI IP, which includes the xSPI PHY IP combines ease of use with high reliability, low power and speed under all conditions, including automotive applications.

XSPI IP

- xSPI - PSRAM Master

- xSPI NOR Flash controller

- xSPI Flash Memory Controller

- XSPI Controller IP

- SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption)

- MIPI-I3C Combo IP Host/Target HDR-DDR compliance with Spec v1.1.1