You are here:

Wide-band Analog-to-Digital Converter

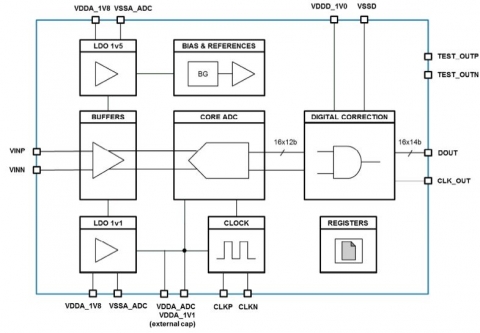

This is a wide-band Analog-to-Digital Converter based on 16 Time-Interleaved Pipeline sub-ADC followed by a digital correction algorithm for gain, offset and skew correction. The differential input is terminated by a 100 Ohms resistor (100 Ohms differential) and followed by an input buffer driving the sub-ADC. The signal amplitude is 1Vpp differential. The analog source driving the ADC shall be ac-coupled to the input pins with two external capacitors of 1nF minimum. The input common-mode is generated internally. The input clock is a differential signal with amplitude of 800mVpp differential.

The ADC includes two internal power supply regulators (LDO) for the analog part:

- A 1.1v LDO with external decoupling capacitor to reach a high power rejection ratio

- A 1.5v LDO with internal capacitor for the input buffer and biasing.

The digital part is supplied by the external 1.0V.The digital corrector receives the 16 sub-ADC 12b outputs and delivers 14b for each output. Hence, the output data are organized in 16x14b–buses clocked at 270MHz (Fs/16). Each bus gives the data coming from a specific sub-ADC in a 2’s complemented format (range is [-2N-1; 2N-1-1]). A data ready clock is provided at 270MHz (Fs/16).

The ADC includes two internal power supply regulators (LDO) for the analog part:

- A 1.1v LDO with external decoupling capacitor to reach a high power rejection ratio

- A 1.5v LDO with internal capacitor for the input buffer and biasing.

The digital part is supplied by the external 1.0V.The digital corrector receives the 16 sub-ADC 12b outputs and delivers 14b for each output. Hence, the output data are organized in 16x14b–buses clocked at 270MHz (Fs/16). Each bus gives the data coming from a specific sub-ADC in a 2’s complemented format (range is [-2N-1; 2N-1-1]). A data ready clock is provided at 270MHz (Fs/16).

查看 Wide-band Analog-to-Digital Converter 详细介绍:

- 查看 Wide-band Analog-to-Digital Converter 完整数据手册

- 联系 Wide-band Analog-to-Digital Converter 供应商