You are here:

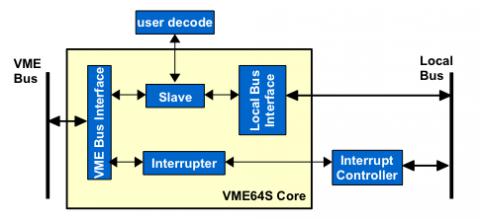

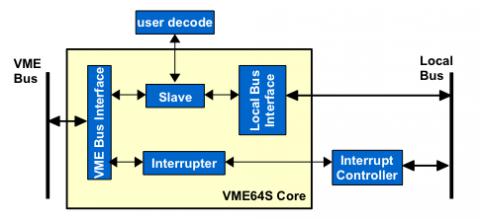

VME Slave Controller

This VME Slave Controller is designed for custom integration using standard FPGA and ASIC technologies. It is fully compliant to the VME specification supporting A16/A24/A32 address mode, D8/D16/D32 data modes (read/write/read-modify-write), D16-BLT, D32-BLT, D64-MBLT, as well as interrupt acknowledge cycles. VMEbus timing is guaranteed by using a system clock of 40 MHz or higher. A synchronous design approach is used to simplify inter- facing to the asynchronous VMEbus. The user side interface is full synchronous. Data access is either single cycle or multi-cycle controlled through user wait states.

To support VME slave controller implementations that do not require the full 32-bit address and data bus width, different top-levels are available. Features such as BLT and MBLT can individually be selected to achieve gate-count optimized implementations.

To support VME slave controller implementations that do not require the full 32-bit address and data bus width, different top-levels are available. Features such as BLT and MBLT can individually be selected to achieve gate-count optimized implementations.

查看 VME Slave Controller 详细介绍:

- 查看 VME Slave Controller 完整数据手册

- 联系 VME Slave Controller 供应商

Block Diagram of the VME Slave Controller