You are here:

Viterbi Decoder

Lattice's Viterbi Decoder is a parameterizable IP core with an efficient algorithm for decoding different combinations of convolutionally-encoded sequences. (Convolutional encoding is a process of adding redundancy to a signal stream in order to increase its robustness.) In the decoder, the convolutional coded sequences that have been corrupted by channel noise, are decoded back to the original sequence.

Many digital transmit-receive systems use a Viterbi decoder for decoding the convolutionally coded data. The digital data stream (e.g., voice, image or any packetized data) is first convolutionally encoded, modulated and transmitted through a wired or wireless channel. Noise from various sources is prone to enter into the channel. The data received from the channel at the receiver side is first demodulated and then decoded using the Viterbi decoder. By using both the original stream and the redundant stream, the Viterbi decoder core is able to correct for errors in the data caused by channel noise. The decoded output is equivalent to the transmitted digital data stream.

The decoder core supports various code rates, constraint lengths and generator polynomials. The core also supports soft-decision decoding and is capable of decoding punctured codes.

Many digital transmit-receive systems use a Viterbi decoder for decoding the convolutionally coded data. The digital data stream (e.g., voice, image or any packetized data) is first convolutionally encoded, modulated and transmitted through a wired or wireless channel. Noise from various sources is prone to enter into the channel. The data received from the channel at the receiver side is first demodulated and then decoded using the Viterbi decoder. By using both the original stream and the redundant stream, the Viterbi decoder core is able to correct for errors in the data caused by channel noise. The decoded output is equivalent to the transmitted digital data stream.

The decoder core supports various code rates, constraint lengths and generator polynomials. The core also supports soft-decision decoding and is capable of decoding punctured codes.

查看 Viterbi Decoder 详细介绍:

- 查看 Viterbi Decoder 完整数据手册

- 联系 Viterbi Decoder 供应商

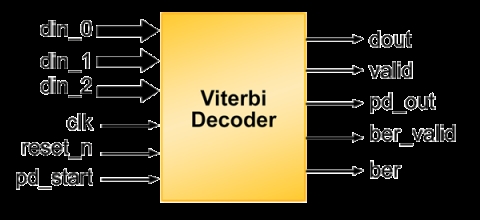

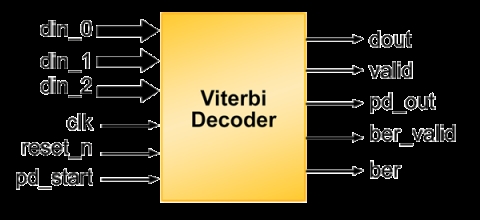

Block Diagram of the Viterbi Decoder

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software