You are here:

Video LVDS SerDes Transmitter / Receiver IP Core

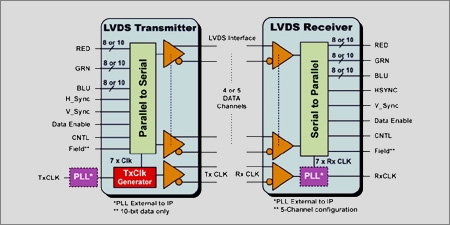

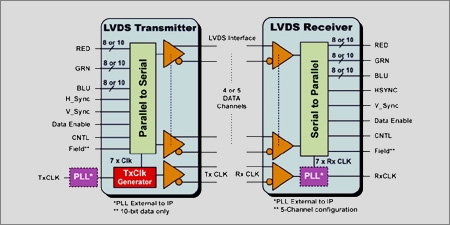

The Video LVDS SerDes Transmitter / Receiver IP Core provides a complete, easy-to-use Serializer/Deserializer (SerDes) solution to interface a wide variety of video host systems to Flat Panel displays.

The Video LVDS SerDes Transmitter / Receiver IP Core simplifies the design of video LVDS interfaces, improves data integrity and timing margins. For example, the Transmitter has the ability to generate a LVDS transmit clock synchronous to the video data stream thereby eliminating the need to fine-tune a PLL to the outputted LVDS data. Similarly, the Receiver auto aligns the receive clock to the encoded video to assure data synchronization. An easy to use GUI enables the user to select the number of LVDS links and to configure the number data channels for each link.

The Transmitter and Receiver cores support both 28 bit (8 bit RGB) and 35 bit (10-bit RGB) parallel data configurations using either 4 or 5 LVDS serial channels. Transmitter and Receiver modules can be cascaded to create dual and quad LVDS links supporting display panel resolutions up to 1080p at 120 Hz and beyond.

The Video LVDS SerDes Transmitter / Receiver IP Core simplifies the design of video LVDS interfaces, improves data integrity and timing margins. For example, the Transmitter has the ability to generate a LVDS transmit clock synchronous to the video data stream thereby eliminating the need to fine-tune a PLL to the outputted LVDS data. Similarly, the Receiver auto aligns the receive clock to the encoded video to assure data synchronization. An easy to use GUI enables the user to select the number of LVDS links and to configure the number data channels for each link.

The Transmitter and Receiver cores support both 28 bit (8 bit RGB) and 35 bit (10-bit RGB) parallel data configurations using either 4 or 5 LVDS serial channels. Transmitter and Receiver modules can be cascaded to create dual and quad LVDS links supporting display panel resolutions up to 1080p at 120 Hz and beyond.

查看 Video LVDS SerDes Transmitter-Receiver IP Core 详细介绍:

- 查看 Video LVDS SerDes Transmitter-Receiver IP Core 完整数据手册

- 联系 Video LVDS SerDes Transmitter-Receiver IP Core 供应商

Block Diagram of the Video LVDS SerDes Transmitter-Receiver IP Core

Serializer/Deserializer IP

- 1.25 Gbps 4-Channel LVDS Deserializer in Samsung 28FDSOI

- Deserializer 1:32 for 8.5-11.3Gb/s for SONET/SDH, 10Ge, XFI, Back Plain

- Serializer 32:1 for 8.5-11.3Gb/s for SONET/SDH, 10Ge, XFI, Back Plain

- 1.25 Gbps Four-Channel (4CH) LVDS Serializer with Pre-emphasis

- Serdes 32:1 for 8.5-11.3Gb/s for SONET/SDH, 10GbE, XFI, Back Plain

- Bi-directional High speed interface lane up to 12.5Gbps