You are here:

视频帧缓冲器

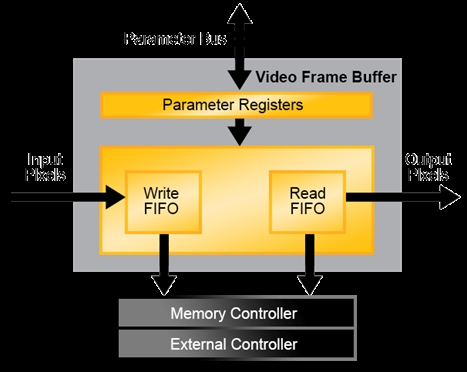

频帧缓冲器IP核将要显示在输出器件,如计算机显示器,投影仪等上的视频数据缓冲到外部存储器。视频帧缓冲器IP核支持最大的图像大小为4Kx4K,YCbCr 4:2:2、4:4:4和RGB视频格式。它通过参数总线支持动态参数更新,总线可以通过配置使用内核提供的不同时钟工作。使用简单的帧速率转换支持不同的输入和输出帧速率。

视频帧缓冲器IP核接收输入的视频数据,存储在外部存储器并且根据dout_enable信号控制的时序进行输出。内核根据应用要求的不同格式宽度将数据存储到存储器中。它还提供了不同时钟域以及不同格式域的数据同步。

内核提供了一个简单的参数总线用于动态更新帧大小。它还实现了一个灵活的存储器接口,可以连接到莱迪思存储器控制器IP核。

内核还通过将外部的两个场(field)结合为一帧来支持隔行扫描。

内核支持从/到外部接口的连续数据流,在不同的时钟域,使用异步写入和读取FIFO。首先输入像素打包和储存到异步双时钟写入FIFO。然后像素将被发送到一个外部存储器控制器,然后写入存储器。当完整的视频帧已存储到外部存储器后,帧读取开始。从外部存储器读取的像素都存储在异步读FIFO并且传输到输出接口时钟域。数据解包后,像素从视频帧缓冲IP核输出。

在视频帧缓冲器中,涉及多个时钟源。存储器接口使用一个单独的存储器时钟。当启用帧速率转换,在视频数据路径上有两个时钟:输入像素采样时钟和输出像素采样时钟。当帧速率转换禁用后,视频数据路径使用输入像素采样时钟速率工作。当启用动态参数更新,参数总线可以配置为使用一个独立的时钟工作。默认情况下,参数总线使用输入像素采样时钟工作。

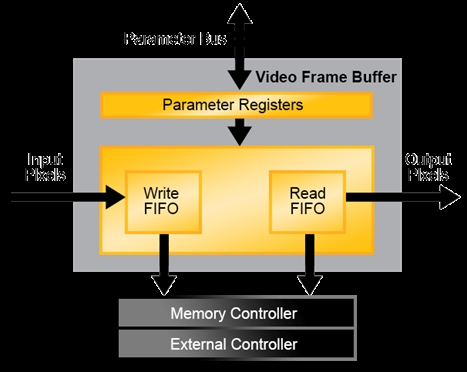

视频帧缓冲器IP核接收输入的视频数据,存储在外部存储器并且根据dout_enable信号控制的时序进行输出。内核根据应用要求的不同格式宽度将数据存储到存储器中。它还提供了不同时钟域以及不同格式域的数据同步。

内核提供了一个简单的参数总线用于动态更新帧大小。它还实现了一个灵活的存储器接口,可以连接到莱迪思存储器控制器IP核。

内核还通过将外部的两个场(field)结合为一帧来支持隔行扫描。

内核支持从/到外部接口的连续数据流,在不同的时钟域,使用异步写入和读取FIFO。首先输入像素打包和储存到异步双时钟写入FIFO。然后像素将被发送到一个外部存储器控制器,然后写入存储器。当完整的视频帧已存储到外部存储器后,帧读取开始。从外部存储器读取的像素都存储在异步读FIFO并且传输到输出接口时钟域。数据解包后,像素从视频帧缓冲IP核输出。

在视频帧缓冲器中,涉及多个时钟源。存储器接口使用一个单独的存储器时钟。当启用帧速率转换,在视频数据路径上有两个时钟:输入像素采样时钟和输出像素采样时钟。当帧速率转换禁用后,视频数据路径使用输入像素采样时钟速率工作。当启用动态参数更新,参数总线可以配置为使用一个独立的时钟工作。默认情况下,参数总线使用输入像素采样时钟工作。

查看 视频帧缓冲器 详细介绍:

- 查看 视频帧缓冲器 完整数据手册

- 联系 视频帧缓冲器 供应商

Block Diagram of the 视频帧缓冲器

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software