You are here:

VESA DisplayPort 1.4 RX IP Subsystem for Xilinx FPGAs

特色

- Complete DisplayPort™ 1.4 Receiver solution with support for VESA Display Stream Compression (DSC)

- Fully compliant with the DisplayPort 1.4a Standard

- Including the DSC slices per line requirements

- Supports up to 4 lanes at HBR3 rate (8.1 Gbits/sec)

- Configurable maximum display resolution up to 8K (FUHD) 60fps in RGB 444

- All color spaces supported by DSC v1.2a and component bit depth up to 12 bits

- Support for Xilinx® UltraScale™ and UltraScale+™ devices

查看 VESA DisplayPort 1.4 RX IP Subsystem for Xilinx FPGAs 详细介绍:

- 查看 VESA DisplayPort 1.4 RX IP Subsystem for Xilinx FPGAs 完整数据手册

- 联系 VESA DisplayPort 1.4 RX IP Subsystem for Xilinx FPGAs 供应商

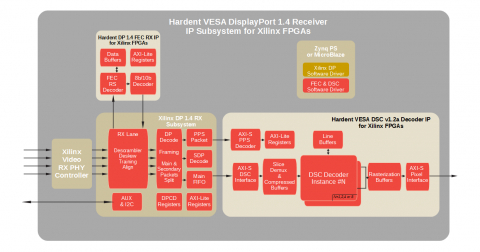

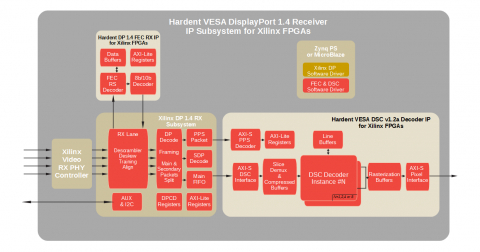

Block Diagram of the VESA DisplayPort 1.4 RX IP Subsystem for Xilinx FPGAs

DisplayPort IP

- HDCP 2.3 Embedded Security Modules on DisplayPort/USB Type-C

- VESA DisplayPort 1.4 Forward Error Correction (FEC) Receiver

- VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

- VESA DisplayPort 2.0 FEC RX

- Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in TSMC 12FFC

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more