You are here:

超高性能的双重配送(Dual issue)处理器,具有高代码密度的优点和静态分支预测器。

超高性能的双重配送(Dual issue)处理器,具有高代码密度的优点和静态分支预测器。

The APS29 from Cortus provides a solution to your performance challenges while staying within stringent power and silicon footprint budgets. A dual issue pipeline gives performance close to a dual core system with only a modest increase in silicon area and power consumption over a similar single issue core. A static branch predictor dramatically improves the performance of loops and the multiply-accumulate feature increases signal processing speeds. These features offer a significant performance boost but require no special programming techniques.

The APS29 is a very high performance, extendible 32 bit microcontroller core featuring a dual issue pipeline ensuring very high integer throughput. The dual issue pipeline provides instruction level parallelism and increases performance without any requirements to change coding styles or complex compilation schemes. All the performance increases are managed within the processor core and require no effort from the programmer.

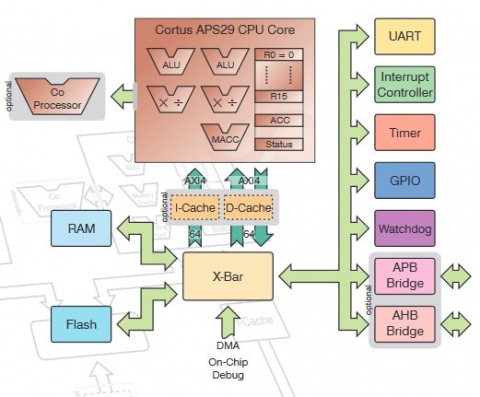

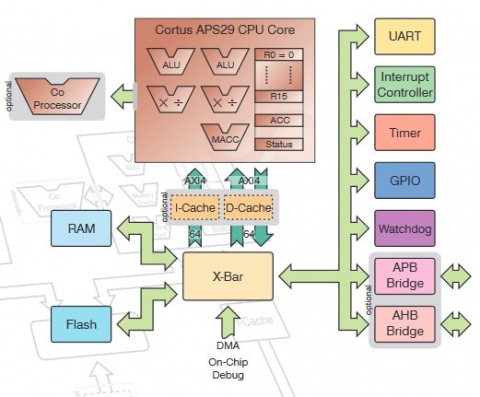

The dual functional units contain a single cycle ALU and multiplier/divider each, and there is one multiply-accumulate unit with a 64 bit accumulator. The load/store unit can coalesce reads and writes onto the 64 bit data bus.

The APS29 from Cortus provides a solution to your performance challenges while staying within stringent power and silicon footprint budgets. A dual issue pipeline gives performance close to a dual core system with only a modest increase in silicon area and power consumption over a similar single issue core. A static branch predictor dramatically improves the performance of loops and the multiply-accumulate feature increases signal processing speeds. These features offer a significant performance boost but require no special programming techniques.

The APS29 is a very high performance, extendible 32 bit microcontroller core featuring a dual issue pipeline ensuring very high integer throughput. The dual issue pipeline provides instruction level parallelism and increases performance without any requirements to change coding styles or complex compilation schemes. All the performance increases are managed within the processor core and require no effort from the programmer.

The dual functional units contain a single cycle ALU and multiplier/divider each, and there is one multiply-accumulate unit with a 64 bit accumulator. The load/store unit can coalesce reads and writes onto the 64 bit data bus.

查看 超高性能的双重配送(Dual issue)处理器,具有高代码密度的优点和静态分支预测器。 详细介绍:

- 查看 超高性能的双重配送(Dual issue)处理器,具有高代码密度的优点和静态分支预测器。 完整数据手册

- 联系 超高性能的双重配送(Dual issue)处理器,具有高代码密度的优点和静态分支预测器。 供应商

Block Diagram of the 超高性能的双重配送(Dual issue)处理器,具有高代码密度的优点和静态分支预测器。

CPU IP

- High Bandwidth Out-of-Order RISC-V CPU IP Core

- All in one solution for AI in RISC-V

- 2D (vector graphics) GPU IP Further advanced architecture for minimized CPU load and increased pixel performance in vector processing

- 2D (vector graphics) & 3D GPU IP A GPU IP combining 3D and 2D rendering features with high performance, low power consumption, and minimum CPU load

- High Bandwidth In-Order RISC-V CPU IP Core

- RISC-V Processor - RV12 - 32/64 bit, Single Core CPU