You are here:

USB3.2 Retimer Controller

MosChip USB3.2 Retimer softcore is designed for use USB Port/Cable Retimer applications with USB SuperSpeedPlus/SuperSpeed link operations The IP has been verified in simulation and is synthesis clean for FPGA implementations. The core is highly power efficient for port or cable retimer applications

查看 USB3.2 Retimer Controller 详细介绍:

- 查看 USB3.2 Retimer Controller 完整数据手册

- 联系 USB3.2 Retimer Controller 供应商

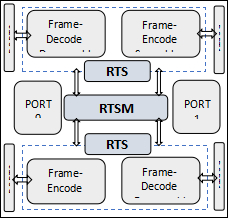

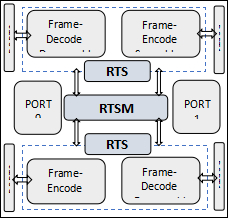

Block Diagram of the USB3.2 Retimer Controller

USB IP IP

- HDCP 2.3 Embedded Security Modules on DisplayPort/USB Type-C

- USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- Multi-protocol SerDes PMA in FDSOI (GF22FDX FDX 22FDX) - PCIe1 PCIe2 PCIe3 PCIe4 and more

- Complete USB Type-C Power Delivery PHY, RTL, and Software